Înainte de compilare, trebuie să selectați și familia FPGA pentru implementarea dispozitivului proiectat (dacă nu ați făcut acest lucru mai devreme când creați proiectul): Alocări -> Device ..., familia este selectată în câmpul Family.

Dacă proiectul necesar nu a fost deschis înainte ca compilatorul să pornească, atunci acesta trebuie deschis. Pentru a face acest lucru, fie deschideți un fișier al acestui proiect și mergeți la meniul File -> Project -> Set Project to Current File.

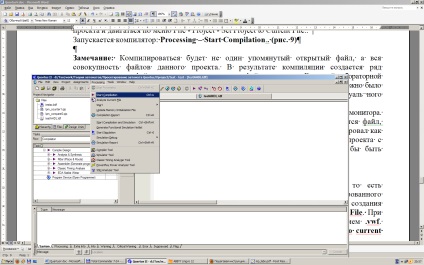

Compilația este pornită de comanda: Processing -> Start Compilation. (Figura 9)

Fig. 9 Executarea compilației

Compilează nu va fi un fișier deschis menționat, ci întreaga colecție de fișiere ale acestui proiect. Ca rezultat, se creează un număr de fișiere auxiliare care nu se referă la fișierele proiectului.

Proiectul trebuie să aibă un fișier cu numele pe care l-ați specificat drept entitatea de design de nivel superior (în exemplul nostru, test). De exemplu, un fișier de schemă sau o descriere AHDL. Acesta va fi modulul de vârf al proiectului dvs. În caz contrar, compilatorul va genera o eroare: Top-Leveldesignentity "file_name" este undefined.

4 Verificarea proiectului

Următorul pas după compilare este verificarea proiectului, adică modelarea și verificarea funcționării corecte a dispozitivului proiectat.

După compilare, trebuie să creați o listă specială pentru simularea funcțională. Selectați elementul de meniu Procesare-> GenerareFuncțională simulareNet. Simularea este temporară și funcțională. Simularea funcțională vă permite să verificați logica muncii. Cu ajutorul său, putem asigura că proiectul poate și ar trebui să funcționeze așa cum a fost intenționat. Mai întâi de toate, trebuie să faceți o simulare funcțională. Simularea temporară vă permite să vedeți semnalele luând în considerare toate întârzierile semnalului dintre elemente, intrări și ieșiri. Simularea temporară se face ultima dată după simularea funcțională, pentru a vă asigura că circuitul poate funcționa la o anumită frecvență. Pentru proiectele mici, este suficient să se efectueze doar o simulare funcțională.

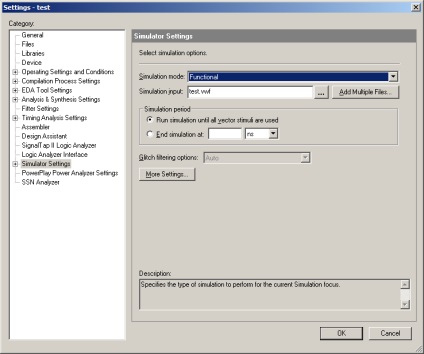

Pentru a specifica tipul de simulare, utilizați elementul de meniu Atribuire -> Setări. În caseta de dialog Setări, este selectată secțiunea Setări simulator. Aici trebuie să specificați tipul de simulare -Funcțional. funcțional. Specificați numele fișierului de intrare de simulare * .vwf. faceți clic pe OK. Acum, totul este gata pentru simulare (Figura 10).

Fig. 10 Simulări de setare

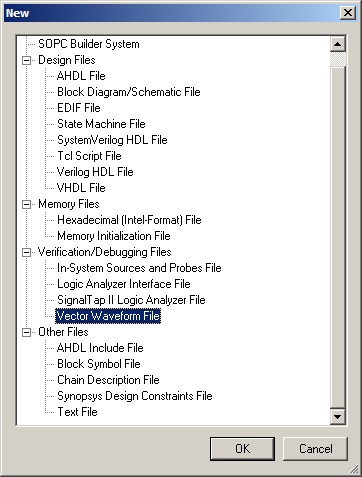

Aceste setări se pot face, de asemenea, după crearea fișierului grafic. În acest caz, pentru a verifica proiectul, trebuie să accesați meniul File -> New -> Verification / DbuggingFiles-> File Waveform. (Figura 11)

Fig.11 Crearea unui fișier grafic de timp

Articole similare

-

Pe un grajd mic au prezentat un proiect de basm pentru adulți și copii

-

Cu mâinile lor, 40 de proiecte de lumină pentru decorarea toamnei casei

Trimiteți-le prietenilor: