E

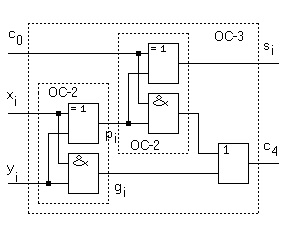

Fig. 73. Modificarea OS-3.

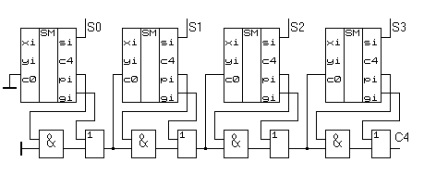

Fig. 74. Construirea unui lanț de transfer accelerat.

În ultima expresie, ggi apare când transferul într-o anumită descărcare este determinat de o combinație a variabilelor de intrare. Prin urmare, g se numește funcția de generare a transferului. Variabila - indică dacă transferul primit în biți de ordin mic este transmis și este numit funcția de propagare a transferului. Ultima expresie arată că sunt necesare două elemente pentru implementarea circuitului transferului: 2I și 2I5. Construcția unui lanț de transfer accelerat pentru un adaos de patru biți este prezentată în figura 74. În figură, lanțurile variabilelor de intrare nu sunt arătate, dar este prezentată numai construcția lanțului de transfer accelerat. Ordinea redusă este în partea stângă. Cu un număr mare de operanzi, circuitul de transfer accelerat permite o creștere semnificativă a vitezei impulsurilor.

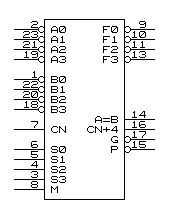

Dispozitiv logic aritmetic.

Pentru a spori funcționalitatea unităților de calcul computerizate, s-au dezvoltat dispozitive electronice combinaționale care permit efectuarea unui anumit set de operații aritmetice și logice. Aceste dispozitive sunt numite dispozitive logice aritmetice (ALU). În seria TTL, ALU a primit un cifru - XXXIP3. Figura 75 prezintă imaginea ALU. După cum se vede în figură, operațiunile sunt efectuate peste operanzi chetyrohrazryadnymi A și B, rezultatul obținut la ieșirea F. Cipul are cinci intrări de control - S și M, respectiv, și 32 efectuează operații aritmetice și logice. Operațiile aritmetice sunt executate cuvânt cu cuvânt, adică luând în considerare transferurile și împrumuturile, iar operațiile logice sunt efectuate în mod biologic. Există o intrare de transfer de la cea mai puțin semnificativă cifră CN și o ieșire de transfer la cifra superioară CN + 4, care permite construirea schemelor ALU multi-bit cu numărul de cifre multiplu de patru. Atunci când se efectuează operații aritmetice generate variabile de ieșire G și P, care permite utilizarea mai multor cipuri pentru a construi circuitul accelerat de transfer. În plus, există o ieșire A = B, semnalul la această ieșire este activ când operanzii sunt egali.

Articole similare

-

Schema - transfer accelerat - enciclopedie mare de petrol și gaze, articol, pagina 1

-

Mânere pentru transfer de bărci, percuție pentru bărci gonflabile

Trimiteți-le prietenilor: