Quartus II. Partea 4. Elemente de logică combinată. Counter.

Din punct de vedere istoric, pentru a descrie circuite digitale, unii

elemente care conțin ambele tipuri de logică, combinatoriale și registru.

Prin urmare, ar fi bine, pe de o parte, să cunoașteți funcționalitatea acestora, pe de altă parte, să știți ce vor fi compilate cu un quarto.

Luați în considerare un exemplu simplu, un sincron "SR" -trigger descris de primitivul "SRFF":

Dacă pe intrarea "S" există un semnal activ. la ieșire. pe partea din față a mantalei, va fi setată la "1".

Dacă există semnal activ la intrarea "R", pe ieșire. pe partea din față a mantalei, va fi setat "0".

Dacă există simultan două semnale. pentru fiecare mantie, declanșatorul își va schimba starea la contrariul. În absența ambelor semnale, starea de la ieșirea declanșatorului nu se va schimba.

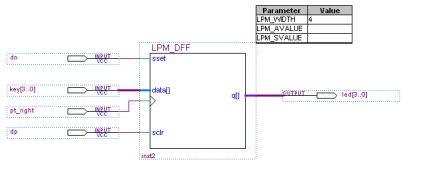

Aproximativ aceeași logică combinatorice și pentru același scop (registrul de setare a situației într-un anumit stat) vor fi adăugate de compilator în megafunctions „LPM_DFF“, în cazul în care proprietățile elementului adăuga intrări „piste sset“ și „sclr“ (setare sincron și resetare sincron):

Dacă există semnal la intrarea "sset". toate declanșatoarele. pe partea din față a mantalei, va fi setată la "1".

Dacă există semnal la intrarea "sclr". toate declanșatoarele. pe partea din față a mantalei, va fi setată la "0".

În absența ambelor semnale, datele de intrare vor fi înregistrate în registru.

Dacă există două semnale "sset" și "sclr" simultan, spre deosebire de primitivul "SRFF"

prioritatea este "sclr", iar toate declanșatoarele vor fi setate la "0".

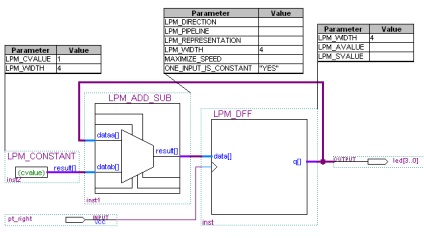

Un alt exemplu de logică combinată este contorul.

Dacă folosim construcții deja familiare. simplu de patru cifre

contorul poate fi reprezentat după cum urmează:

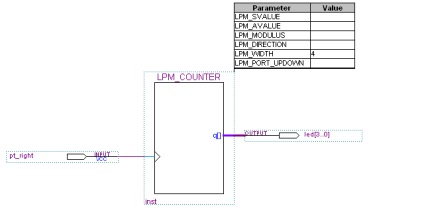

După cum se poate observa din diagrama, funcționează după cum urmează, funcția „LPM_ADD_SUB“ la ieșire existent „LPM_DFF“, adaugă numărul de registru constant „1“. Astfel, pentru fiecare clonă a frecvenței ceasului, valoarea "1 care depășește valoarea precedentă va fi înregistrată în registrul" LPM_DFF ". Adică numărul de clustere va fi calculat. Implementați aceeași funcționalitate cu ajutorul megafuncției "LPM_COUNTER":

Deoarece contorul este un element foarte frecvent utilizat, voi descrie câteva proprietăți

megafuncțiile "LPM_COUNTER" în detaliu:

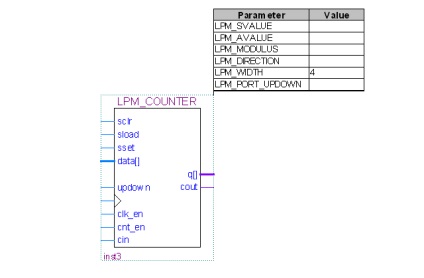

intrări:

- "sset" și "sclr" au același efect ca în cazul "LPM_DFF". și anume setați sau resetați toate declanșatoarele.

- „Sload“ utilizat împreună cu „datele []“ și seturi toate flip-flop la starea existentă la intrare „date []“. (Dacă „datele []“ de intrare este absent, se va încărca „0“ pentru „sload“). Dintre aceste trei intrări au cea mai mare „sclr“ prioritate, apoi „sload“, minimum - „piste sset“.

- "updown" - controlul direcției contului. Dacă "updown" este "1", atunci pentru fiecare ciclu de numărare valoarea contorului va crește. dacă "0" scade. Dacă această intrare nu este disponibilă, direcția contului poate fi setată în parametrul "LPM_DIRECTION" (implicit este "UP").

- "clk_en" rezoluție de mantie. Lipsa unui semnal activ pe această intrare interzice orice operațiuni cu declanșatoare.

- "cnt_en" și "cin" sunt intrări echivalente. Ele controlează numai ciclurile de numărare și nu afectează operațiile "sload", "sset" și "sclr".

- Ieșirile "q []" - de fapt. bucăți de contor. Numărul lor (adâncimea de biți) este indicat în "LPM_WIDTH"

- Ieșirea "cout" este o transportare. Dacă parametrul "LPM_MODULUS" este absent sau egal cu "0", semnalul "cout" va fi activ dacă ieșirea contorului este totală "1".

Dacă parametrul „LPM_MODULUS“ are o anumită valoare, „cout“ va fi activ atunci când valoarea contorului cu 1 este mai mic decât „LPM_MODULUS“ și pe următorul ciclu de numărare „0“ este încărcat în tejghea.

În concluzie, vreau să spun că, în opinia mea, informațiile conținute în această mică serie de articole sunt suficiente pentru a pune în aplicare orice proiect pentru roverul Mars.

Cum de a extinde pulsul cu FPGA?

Există 1kHz 2mks, aveți nevoie de 1kHz 50mks.

Nu sunt sigur că puteți da un răspuns bun la această întrebare, deoarece sarcina nu este complet clară.

Cea mai ușoară cale este să "polonezi" semnalul cu o frecvență foarte înaltă. Deci, puteți detecta frontul cu o anumită eroare, apoi numărați numărul specificat de măsuri pe frecvența [cenzurată] de înaltă frecvență și acesta va fi sfârșitul unui impuls larg. Cu această metodă, desigur, faza pulsului larg de ieșire va fi ușor agitată față de cea inițială. Nu este ușor să faci un expander de impuls cu păstrarea fazei, dacă este posibil.

Cum de a extinde pulsul cu FPGA?

Există 1kHz 2mks, aveți nevoie de 1kHz 50mks.

Trimiteți-le prietenilor: