Semiconductorii IC sunt fabricați prin formarea unei structuri IC într-un corp semiconductor cu un singur cristal prin intermediul operațiilor tehnologice. Se creează diverse regiuni care au o conductivitate electronică (regiune p) și o regiune (n-regiune). Regiunile formate din semiconductor corespund în funcție de anumite elemente: active (tranzistor, diodă) și pasive (rezistor, condensator etc.). Calele volumetrice de transport ale curentului sunt create prin aplicarea unui strat invers de conductivitate ridicată pe suprafața semiconductorului. Un astfel de IC semiconductor poate fi o construcție completă a unui produs microelectronic, i. E. proiectarea unui circuit electric care realizează direct parametrii și caracteristicile acestui circuit.

Implementarea și proiectarea documentației de proiectare a IC semiconductoare sunt reglementate de standardele ESKD și de standardele industriale. Setul de bază al documentației de proiectare pentru IC include specificații, schema electrică de bază (EZ), ansamblul topologic și desenele stratificate ale produsului (SB). formularul de brevet (PF), o hartă a nivelului tehnologic și a calității produsului

(CG), fișa de referință (D1) și eticheta 07).

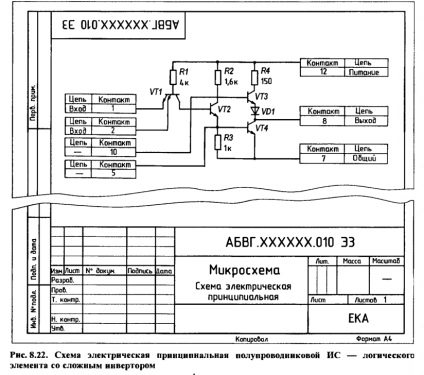

Procesul de construire a microcircuitului începe cu dezvoltarea unei scheme electrice (EZ). În Fig. 8.22 este o diagramă a unui element logic al logicii tranzistor-tranzistor cu un invertor complex. Toate elementele au desemnări alfanumerice grafice în conformitate cu GOST ESDD. Tranzistorii sunt arătați fără o carcasă. Denumirile alfanumerice sunt atribuite tuturor elementelor în serie, indiferent de designul elementului (semiconductori, benzi, film). Ieșirile, intrările și contactele de alimentare din circuit sunt aranjate într-un rând, în acest caz - vertical. În plus față de desemnarea grafică convențională a elementelor, sunt indicate denumirile, toleranțele și alte date. În acest caz, lista elementelor nu este dezvoltată. Pe baza circuitului electric, pe mai multe coli este realizat un desen topologic. Desenele topologice sunt realizate pe o scară de extindere de 100: 1; 200: 1; 400: 1, care vă permite să obțineți un aspect clar al elementelor. Pe prima pagină (vizualizarea principală) este prezentat un substrat cu toate straturile (elementele) aplicate.

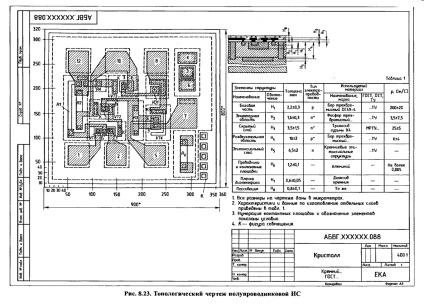

Pe imaginea substratului, trebuie realizate figuri de aliniere care sunt tehnologice (Figura 8.23). Cifrele de aliniere pot avea diferite forme: triunghiulare, dreptunghiulare, cruce, etc. Figurile corespunzătoare alinierii sunt prezentate pe straturi separate. Zonele de contact sunt realizate sub formă de poligoane, umbrite și numerotate, pornind de la colțul din stânga jos în direcția acelor de ceasornic. Zonele interioare sunt numerotate de sus în jos și de la stânga la dreapta. Pentru comoditatea desenării elementelor chipului în desene topologice, se utilizează o grilă cu o treaptă de 0,01; 0,05; 0,1 sau 0,2 mm. Vârfurile formelor elementelor trebuie să fie amplasate la punctele de intersecție ale liniilor de rețea. În desen, grila nu este afișată și coordonatele sunt reprezentate grafic pe perimetru. Pe lângă executiv, dimensiunile de referință trebuie indicate.

Pe prima foaie a desenului topologic, se face o tăietură complexă treptată prin diferite elemente și componente (poziția planului de tăiere nu este indicată). Grosimea straturilor este notată cu litera H cu indicele numeric corespunzător. Grosimea straturilor pentru claritate nu poate fi menținută. Datele de bază ale straturilor IC sunt indicate în tabelul de pe câmpul de desen. Tabelul poate conține următoarele coloane: "Elemente

structură "," tip de conductivitate electrică "," material utilizat "etc. (a se vedea figura 8.23). Informațiile despre tehnologia de fabricație a IC sunt indicate în cerințele tehnice din domeniul desenului.

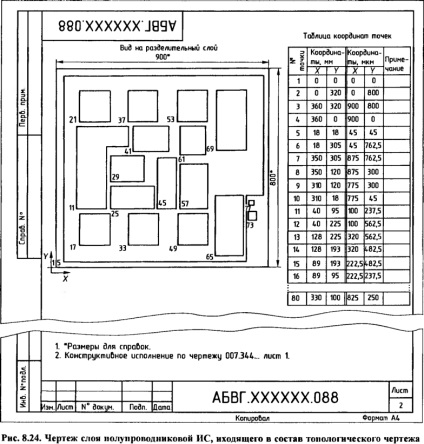

Foi ulterioare ale desenului topologic sunt efectuate separat pentru fiecare strat, inclusiv imaginile conductorilor de legătură și plăcuțele de contact. În Fig. 8.24 este prezentată cea de-a doua foaie a desenului topologic al cristalului. Deasupra imaginii stratului trebuie plasat o inscripție pe tipul "Vedere spre stratul de separare", "Vedere spre stratul de bază" etc. Dimensiunile elementelor sunt specificate folosind grila și tabela coordonatelor.

Fiecare element al IC (poligon) ar trebui să aibă o denumire digitală a vârfului inferior stâng. Numărul 1 este atribuit colului din stânga-jos al dreptunghiului care definește limitele cristalului. Nodurile rămase ale dreptunghiului nu sunt definite, dar se înțelege le numerotarea în sens orar și un tabel de coordonate dă valorile tuturor punctelor dreptunghiului (vezi. Fig. 8.24). Dreptunghiul care determină dimensiunile cristalului este dat de patru puncte (1. 4). Următoarele noduri sunt notate secvențial pentru fiecare element prin dispunerea elementelor de la stânga la dreapta și de jos în sus. Inscripția principală pe următoarele foi se face în conformitate cu formularul 2a GOST 2.104-68 *.

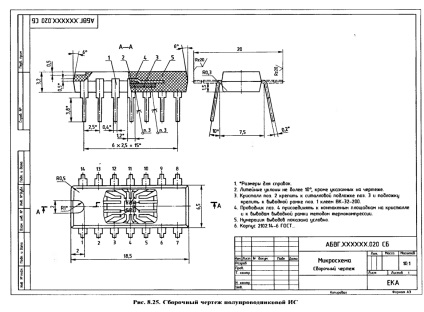

Materialul stratului este dat în tabelul de pe prima foaie a desenului topologic. După finalizarea desenelor topologice ale tuturor straturilor, se începe proiectarea desenului de asamblare (figura 8.25). Desenul este realizat în conformitate cu cerințele GOST 2.109-73 * și standardele industriale. Specificațiile indică informațiile necesare pentru punerea în aplicare a ansamblului și testarea produselor, opțiuni, efectuate sau supravegheate pe desen, informații cu privire la natura componentelor de conectare ale cip, de etanșare, etichetarea, etc. Specificații

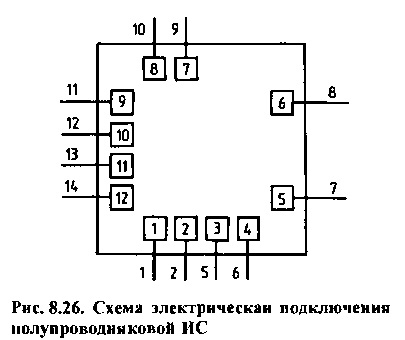

se efectuează în conformitate cu cerințele GOST 2.106-96. Pe ansamblu de desene compus cristal cu PIN-ul carcasă nu este arătat, și constituie schema electrică electrice (fig. 8.26). Celelalte documente de proiectare - desen dimensional, harta la nivel tehnologic și de calitate, formă de brevete, etichete, etc -. Executate în conformitate cu standardele ESKD.

Trimiteți-le prietenilor: