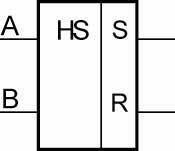

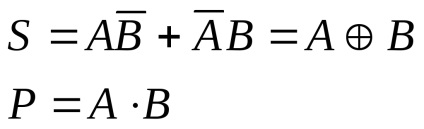

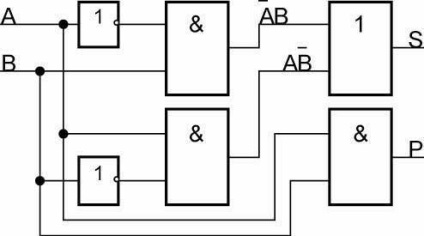

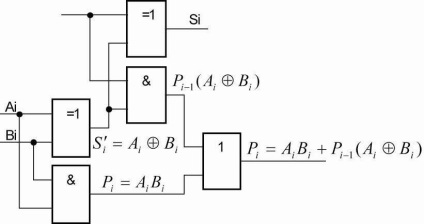

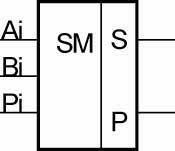

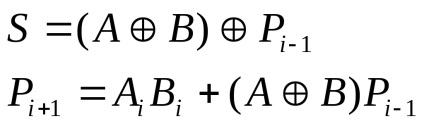

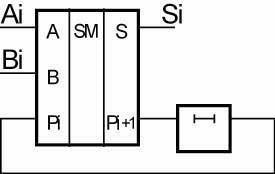

Funcționarea jumătății adder este descrisă de ecuația:

Structura logică a jumătății adderului în forma generală și extinsă

HS are două intrări și, prin urmare, este adecvată pentru utilizare numai în ordine scăzută. Dispozitivul pentru însumarea a două cifre multiplicate trebuie să aibă, începând cu a doua cifră, trei intrări: două pentru sumele

Suma totală poate fi reprezentată ca unitate de două jumătăți. Unul servește pentru adăugarea a două numere care aparțin unei categorii și care oferă o cantitate intermediară

În introducerea secvențială, una comună pentru toate cifrele este un aderent complet cu un circuit de întârziere suplimentar. Ambii termeni sunt codificați prin secvențe de impulsuri, care sunt introduse sincron prin intrările A și B

n

Demnitate - costuri hardware mici.

Dezavantajul este o viteză relativ scăzută.

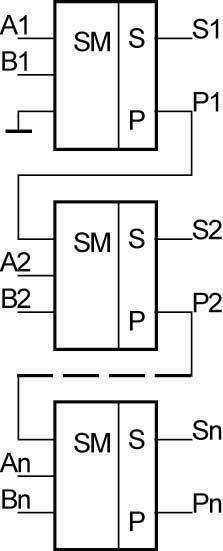

Numărul de aditivi ai unui adder paralel n-bit cu transmisie secvențială este egal cu numărul de cifre.

În

Termenii

Viteza este limitată de întârzierea de transportare până când semnalul de la cel mai puțin semnificativ bit este propagat în întregul sistem.

Timpul de transfer reduce introducerea transportului paralel, care se realizează prin introducerea de blocuri de transfer accelerat (prin).

Pentru fiecare bit, există două semnale suplimentare:

Procesul de formare a transferului accelerat este descris de următoarele ecuații:

Comparatoare digitale (comparatoare)

Comparatoarele digitale (compare-compare) compară două numere date de codul binar (zecimal binar).

În funcție de implementarea circuitului comparatori poate determina egalitatea sau o inegalitate: A = B, A> Bilia> B, gdeAiB- numere independente, cu un număr egal de biți. Rezultatul comparației este afișat corespunzător nivelurilor logice la ieșire.

De regulă, chips-urile digitale de comparare efectuează toate aceste operațiuni și au trei ieșiri.

Pentru a găsi numărul corect (cuvânt) în fluxul informațiilor digitale.

Pentru a marca timpul în ceas.

Pentru a efectua tranziții condiționate în dispozitivele de calcul.

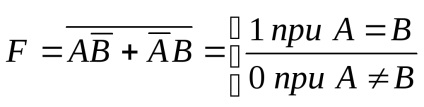

Ca comparator de o singură cifră, poate fi folosit un circuit logic care efectuează operația de echivalență (exclusiv OR-NOT). Cel mai adesea este construit pe baza "exclusive - OR".

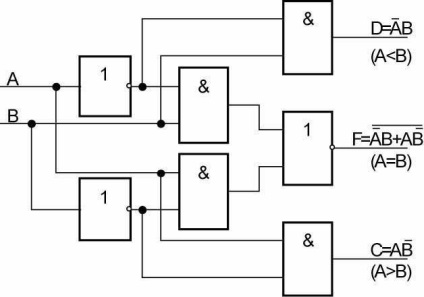

Structura logică extinsă a unui comparator cu un singur bit are forma:

pentru A> B (adică A = 1, B = 0)

la A<В (т.е А=0, В=1)

Două numere binare n-biți sunt egale atunci când toate cifrele acestor numere sunt perechi egale. Dacă chislaAiB- patru cifre, semnul egalității este: A3 = B3; A2 = B2; A1 „= B1; A0 = B0 = ilia BpriF = F3F2F1F0 = 1, esliF = 0, Toa ≠ B.

Inegalitatea A> B este prevăzută în unul din cele patru cazuri:

A3 = B3; A2 = B2; A1> B1;

A3 = B3; A2 = B2; A1 = B1; A0> B0.

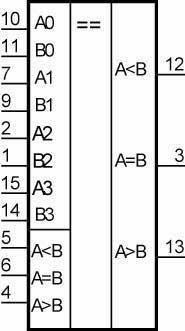

Un exemplu de comparator digital este IS K561IIP2.

Cipul are intrări expandabile, care permit creșterea numărului de cifre ale ambelor numere fără elemente logice suplimentare. (A = B, A> B, A> B)

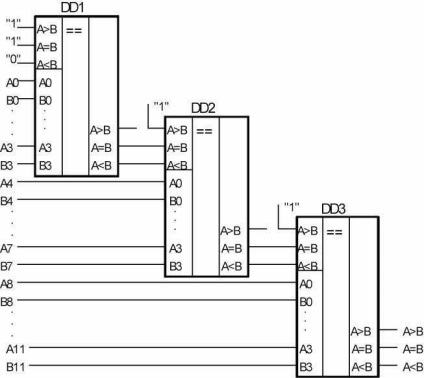

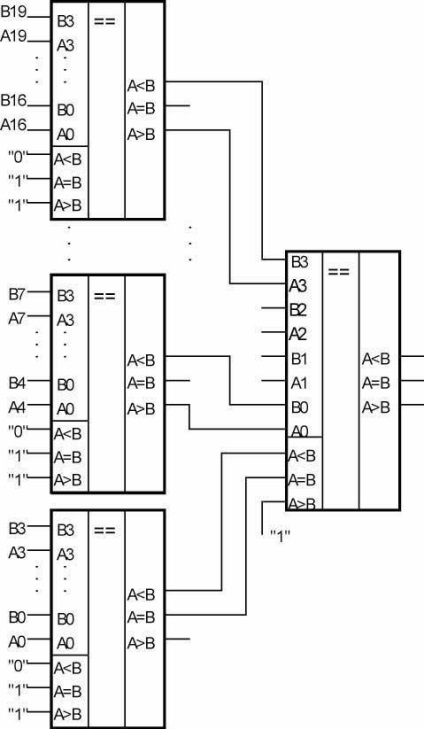

Comparatoarele pot fi conectate în cascadă și paralele.

Cu o conexiune paralelă (piramidal), timpul de întârziere este mai scurt (adică viteza comparatoarelor este mai mare).

Cascadă de comparator digital:

Ieșirile A = B și A

Această operație îmbunătățește fiabilitatea transmisiei informațiilor binare.

O modalitate simplă și eficientă de detectare a erorilor se bazează pe presupunerea că în fiecare moment de timp eroarea poate apărea doar într-o singură cifră și se manifestă într-o unitate suplimentară sau în pierderea unei unități.

Astfel. dacă cuvântul transmis conține un număr par de cifre pentru toate cifrele și la sfârșitul liniei de transmisie acest număr este ciudat, atunci a apărut o eroare.

Această metodă este implementată utilizând scheme de paritate speciale.

Pe baza informațiilor de la ieșirea elementului anterior, circuitul generează un bit suplimentar (paritatea sau bitul de referință), adică "1" sau "0" care se adaugă la informațiile de ieșire.

Atribuirea unui bit de paritate - pentru a aduce numărul de unități din fiecare cuvânt transmis la un even sau ciudat, în funcție de sistemul de codare acceptat.

La capătul de primire al liniei se efectuează o verificare a parității. Dacă este corect, recepția este permisă, dacă nu, indicatorul de eroare este pornit.

Paritatea poate fi par i ciudat.

În cazul parității ciudate, suma unităților, împreună cu bitul de control, trebuie să fie ciudat, iar pentru bitul uniform, contrariul. În practică, paritatea ciudată este folosită mai des, deoarece controlul ciudat vă permite să surprindeți pierderea completă a informațiilor.

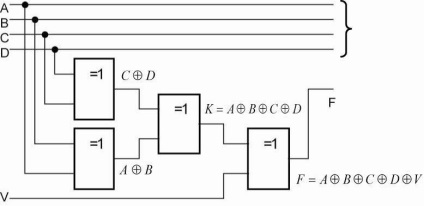

Structura schemei de verificare a parității este în mai multe etape. În prima etapă (tier) toți biții cuvântului sunt însumați în perechi. Semnalele de ieșire din primul nivel sunt introduse în a doua și așa mai departe secvențial până la sfârșitul determinării parității sau ciudățeniei întregului cuvânt.

Rezultatul obținut în ultima etapă este comparat cu un semnal de control care specifică tipul de paritate utilizat.

În cazul în care paritatea este chiar, r. E. Numărul celor într-un cuvânt, inclusiv un pic de paritate trebuie să fie chiar, semnalul de control ar trebui să fie egală cu suma modulo 2 a tuturor biți de informație ale cuvântului. Pentru paritatea ciudată, semnalul de control este inversarea cantității specificate.

Adică, indiferent de paritatea cuvântului ABCD cu patru biți, paritatea codului din cinci cifre ABCDF va fi întotdeauna aceeași.

Potențialul de intrare determină tipul de paritate utilizat.

Un exemplu de produse independente poate servi CMOS IS K561SA1 și TTL K155IP2.

Articole similare

-

5 motive pentru care noul dispozitiv de mere "homepod" nu ma inspirat

-

Sanpin 1600-77 Reguli sanitare ale dispozitivului și întreținerea cimitirelor - descărcare gratuită

Trimiteți-le prietenilor: