Bazat pe articolul lui Thorsten Götselmann, inginer la Keysight Technologies (Thorsten Götzelmann ThorstenG)

Din Wikipedia:

PCI Express. sau PCIe. sau PCI-E (de asemenea, cunoscut sub numele de 3GIO pentru 3-a generație I / O) - autobuz calculator (deși magistrala stratul fizic nu este, fiind un compus de tip „punct la punct“) utilizează un bus de programare model de PCI și protocol fizic ridicat bazat pe transmiterea de date seriale.

Specificații PCI Express

Specificații de bază

Specificații CEM

Cel mai comun model pentru PCI Express este probabil slotul de extensie PCI Express, care este definit în caracteristicile electromecanice ale plăcii PCI Express (CEM). În testarea receptoarelor, trebuie luate în considerare două tipuri diferite de dispozitive: carduri de extensie și placi de bază (sistem). CEM utilizează numai modul sincron de operare și este singurul ecosistem PCI Express care oferă un program de certificare obligatoriu pentru respectarea standardului, inclusiv testele privind stratul fizic. Toate dispozitivele din lista integratorilor PCI-SIG trebuie testate într-unul din laboratoarele de testare PCI-SIG. Testele de conformitate cu stratul fizic solicitate sunt definite în caietul de sarcini al arhitecturii stratului fizic PCI Express (CTS). Testele CTS sunt proiectate astfel încât să poată fi efectuate în laborator.

Ca urmare, testarea receptoarelor în conformitate cu CTS poate să nu fie la fel de strictă și mai puțin complexă decât testarea în conformitate cu specificațiile de bază.

Specificațiile de testare a stratului fizic (M-PHY)

M-PCIe înlocuiește stratul fizic al PCI Express cu stratul fizic definit pentru M-PHY. Prin urmare, testele receptorului trebuie să fie efectuate în conformitate cu specificația M-PHY, nu cu specificația PCI Express. M-PHY este stratul fizic definit de Alianța MIPI®.

Cerințe pentru testarea receptoarelor PCI Express

Cerințele de testare și metodele de calibrare nu sunt aceleași pentru rate diferite de date. În specificația PCIe 3.0, punctul de referință este transferat în interiorul cipului, iar structura semnalului de test distorsionat devine mai complexă. În plus, metodologia utilizată pentru a testa receptoarele, care descriu interferența intersymbol în canal, diferă pentru rate de 2,5 / 5GT / s și 8/16 GT / s.

De asemenea, cerințele de testare determină compatibilitatea înapoi. Adică, un dispozitiv capabil să funcționeze la viteze mai mari ar trebui să fie compatibil și cu rate de transfer mai mici.

PCI Express 2.5 G / s

Specificațiile receptorului sunt definite pe bornele receptorului. Specificațiile sunt identice pentru diferite scheme de sincronizare atât pentru modurile de funcționare sincrone, cât și pentru cele asincrone. Numai o mască simplă a receptorului este definită. Deoarece nu sunt disponibile specificațiile aleatorii ale jitterului (RJ), valorile RJ, determinate pentru o viteză de 5 Gt / s, sunt de obicei utilizate. Testarea pentru caietul de sarcini de bază nu necesită nici un pre-accent, dar testarea în conformitate cu CEM - necesită.

Factorii care determină cele mai grave condiții:

- Interferențe inter-simbol (ISI) printr-un canal extern. Interferențele inter-simboluri ar trebui să fie principala componentă a jitterului determinist (DJ). Pentru testele CEM, aveți nevoie de un card de bază pentru a verifica conformitatea cu PCI-SIG (CBB) și cu o carte de încărcare pentru testul de conformitate (CLB). Cartela CBB pentru gen1 și gen2 ar trebui să fie configurată astfel încât să poată fi utilizată pentru a testa receptoarele

- Jitter aleator (RJ)

- Pentru a asigura închiderea necesară a ochilor, interferența intersymbol este completată de jitter sinusoidal (SJ)

- Interferențe sinusoidale în fază (CM-SI), numai pentru specificațiile de bază

PCI Express 5 G / s

Specificațiile receptorului sunt de asemenea definite pe bornele receptorului. Specificațiile de bază definesc diferiți parametri pentru receptoare utilizând CC sau DC. Specificațiile CEM nu se aplică CM-SI, dar se adaugă un al doilea ton de jitter de înaltă frecvență. Pentru scenariile de aplicare CC, este definit un SSC rezidual (rSSC); rSSC este o modulație triunghiulară de fază aplicată numai unui semnal de încercare distorsionat, dar nu unui ceas de referință. Acesta determină cele mai grave condiții în care poate exista un receptor între ceasul de referință al SSC și SSC a semnalului de intrare.

Factorii care determină cele mai grave condiții:

- Interferențe inter-simboluri prin intermediul unui canal extern. Interferențele inter-simboluri ar trebui să fie principala componentă a jitterului obișnuit. Pentru testele CEM, aveți nevoie de un card de bază pentru a verifica conformitatea cu PCI-SIG (CBB) și cu o carte de încărcare pentru testul de conformitate (CLB). Cartela CBB pentru gen1 și gen2 ar trebui modificată astfel încât să poată fi utilizată pentru a testa receptoarele.

- Spectru-filtrată aleatoare jitter (sRJ), cu o amplitudine mai mare pentru spectrul de frecvențe de până la 1,5 MHz și o amplitudine mai mică pentru spectrul de frecvență de la 1,5 la 100 MHz

- Pentru a asigura închiderea necesară a ochilor, interferența intersymbol este completată de jitter sinusoidal (SJ)

- SSC:

- rSSC este utilizat pentru implementările bazate pe CC, pe lângă sistemele de testare bazate pe CEM, deoarece SSC este determinată de viteza ceasului sistemului

- SSC este utilizat pentru implementările bazate pe DC

- CM-SI, numai pentru specificațiile de bază

- SJ secundar de înaltă frecvență numai pentru specificațiile CEM

PCI Express 8 G / s

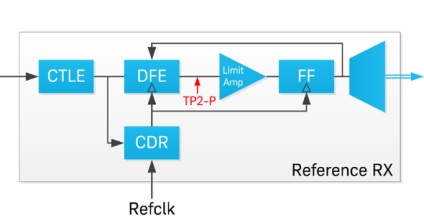

Fig. 1. Punct de referință TP2-P, definit în specificațiile receptorului PCIe 8 Gt / s

Viteza de transmisie mărită, practic, de-a lungul aceluiași canal, face necesară corecția receptorului, prin urmare, testarea receptorului devine foarte importantă. Specificațiile receptorului sunt descrise mai detaliat și definite în interiorul receptorului după corectorii (CTLE și DFE). Acest punct de referință se numește TP2-P. Datorită schimbării determinării punctului de referință, pentru a calibra semnalul de încercare distorsionat, este necesar să se utilizeze integrarea pachetului de comportament al receptorului, precum și simularea circuitelor de corecție și restaurarea frecvenței ceasului.

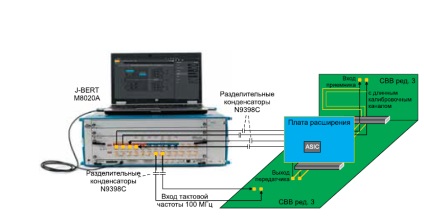

Fig. 2. Exemplu de circuit pentru testarea receptorului cardului de expansiune PCIe 8 Gt / s

Factorii care determină cele mai grave condiții:

- Interferențe inter-simboluri prin intermediul unui canal extern. Pentru testele CEM, aveți nevoie de un card de bază pentru testul de conformitate PCI-SIG (CBB), un adaptor și o placă de încărcare pentru potrivirea (CLB) pentru gen3 pentru un canal lung și CBB gen2 pentru un canal scurt

- Randament jitter cu un filtru de trecere de 10 MHz

- Jitter sinusoidal, diferite măști de toleranță la jitter pentru CC și SRNS / SRIS

- SSC, SRIS numai:

- Distribuția triunghiului la partea de jos la 33 kHz pentru testarea cu o tensiune limitată

- Distribuția sinusoidală la partea de jos la 33 kHz pentru testarea cu jitter limitator

- DM-SI

- CM-SI, numai pentru specificațiile de bază

După îmbunătățirea capacităților fizice ale receptoarelor PCIe, optimizarea corecției transmițătorului a fost adăugată procedurii de formare a canalelor, care ia în considerare caracteristicile canalului curent, transmițătorului și receptorului.

PCI Express 16 G / s

PCI Express generație 4 va sprijini o viteză de 16 Gt / s. Specificațiile 4.0 nu au fost încă lansate și lucrările sunt în desfășurare. Încă de lucru de grup PCI-SIG, care lucrează la versiunea 4.0 și specificațiile receptorului 16 GT / s, cel mai probabil, va urma metoda receptoarelor de calibrare 8 GT / s, cu îmbunătățiri menite să îmbunătățească compatibilitatea între circuitele de testare diferite. Reglarea lățimii și înălțimii ochiului peste bruiaj aleatoare și receptorul DM-SI în timpul calibrării PCIe 8 GT / s în combinație cu o bandă de toleranță pe canalul de ± 2 dB, probabil să fie problematică. Schemele cu pierderi mai mici pot necesita un jitter semnificativ mai mare pentru a închide ochiul la valorile specificate în comparație cu schemele cu pierderi mari. Dar, de cele mai multe receptoare face față mai bine cu interferența inter-simbol cauzate de pierderi în canal decât bruiaj aleatoare, și ca urmare a celor două sisteme de măsurare pot crea condiții de testare inconsistente. Pentru a remedia această situație, standard toleranțele de strângere pentru canalele de testare, care necesită un fel de configurare interferența inter-simbol, de exemplu, prin selectarea carduri de canal cu valoare diferită de inter-simbol interferențe.

Factorii preliminari care determină cele mai grave condiții:

- Interferențe inter-simboluri printr-un canal extern selectabil sau selectabil. Testarea CEM este probabil să necesite utilizarea platformelor de testare dezvoltate și furnizate de PCI-SIG

- Randament jitter cu un filtru de trecere de 10 MHz

- Jitter sinusoidal, diferite măști de toleranță la jitter pentru CC și SRNS / SRIS

- SSC, SRIS numai:

- Distribuția triunghiului la partea de jos la 33 kHz pentru testarea cu o tensiune limitată

- Distribuția sinusoidală la partea de jos la 33 kHz pentru testarea cu jitter limitator

- DM-SI

- CM-SI, numai pentru specificațiile de bază

Verificarea corecției canalelor

Testele de corecție a canalelor pot diferi pentru receptoare și transmițătoare. Teste receptoare nu diferă de la receptoarele teste clasice, cu excepția faptului că receptorul DUT „este de acord“ cu transmițătorul corecției frecvenței OARET și stabilirea caracteristicilor de ridicare pre folosite pentru a testa acest receptor. Calibrarea unui semnal de încercare distorsionat este identică cu testul clasic al receptoarelor de 8 Gt / s.

Testarea corecției canalului de transmițător se concentrează pe doi factori:

- Forma de undă reală, bazată pe cererile partenerului de canal. Aceasta include modificări ale formei de undă actuale și asigură, de asemenea, că semnalul îndeplinește cerințele specificațiilor țintă

- Timp de răspuns pentru solicitările de modificare din partea partenerului prin intermediul canalului. Se compune din momentul răspunsului logic și din momentul răspunsului fizic. Timpul de răspuns logic este timpul dintre solicitarea de modificare și trimiterea confirmării către partener, în timp ce timpul de răspuns fizic este timpul de la solicitarea de modificare până la modificarea efectivă a formei de undă.

concluzie

Cu fiecare ediție nouă, standardul PCI Express extinde limitele capacităților de transfer de date ale canalelor implementate pe plăcile din fibră de sticlă FR4 și, prin urmare, receptoarele devin din ce în ce mai complexe. Ca urmare, este necesar să se utilizeze echipamente de control și măsurare cu un set mare de capabilități și scheme de testare mai complexe. Producătorii de echipamente de control și măsurare sunt obligați să răspundă acestor cerințe noi. Un bun exemplu este dezvoltarea sistemelor BERT de către Keysight Technologies. De exemplu, sistemul JERT M8020A BERT demonstrează integrarea componentelor BERT clasice într-un singur dispozitiv, care permite obținerea de noi caracteristici, cum ar fi LTSSM, care vizează depășirea unor noi dificultăți de testare.

PCIe și PCI Express sunt mărci comerciale înregistrate ale PCI-SIG®.

MIPI este o marcă înregistrată a MIPI, Inc. în Statele Unite și în alte țări.

rezultate

Articole similare

Trimiteți-le prietenilor: