Bazat pe JK-flip-flops și D-flip-flops, este posibil să se construiască circuite care efectuează așa numitul mod de numărare. Astfel de scheme sunt numite T-flip-flop-uri sau numărătoare de flip-flops, care leagă astfel modul în care funcționează.

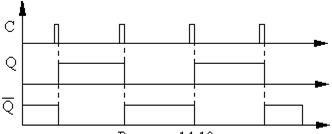

În Fig. 16 prezintă schema de organizare a flip-flopului T bazat pe jgheaburi JK și D. Modul de numărare este ilustrat de diagramele de timp din Fig. 17.

JK-flip-flop la intrările unui mod de numărare de reglare la zero logic se realizează prin alimentarea constante J = K = 1 și R = S = 1 și intrare T la intrare C. în conformitate cu tabelul de funcționare la fiecare margine negativă a semnalului de intrare T flip-flop își schimbă starea adică contrariul.

În flip-flopul D, modul de numărare se realizează prin intermediul unui feedback (semnalul de la ieșirea inversă este alimentat la intrarea D). Astfel, există întotdeauna o inegalitate a semnalului la intrarea D și semnalul la ieșirea Q. dacă Q = 1, D = 0. Prin urmare, pentru fiecare scădere a semnalului pozitiv la intrarea de numărare C, în conformitate cu principiul funcționării declanșatorului D, starea de ieșire se va schimba la opusul.

Astfel, pentru fiecare două impulsuri de ceas de intrare, flip-flopul T generează o perioadă a semnalului de ieșire Q. Prin urmare, flip-flop-ul efectuează o diviziune de frecvență în cursul a 2:

,

unde este rata de repetare a impulsului la ieșirea flip-flop-ului.

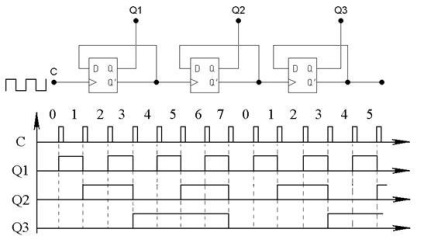

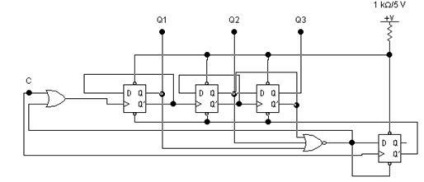

Counter - un dispozitiv pentru numărarea numărului de impulsuri de intrare. Numărul reprezentat de starea ieșirilor sale de-a lungul frontului fiecărui impuls de intrare este schimbat cu unul. Contorul poate fi implementat pe mai multe jgheaburi JK sau D, iar declanșatoarele trebuie să funcționeze în modul de numărare. În numărarea contoarelor, fiecare impuls de intrare mărește numărul la ieșirea lui cu unu, în scăderea numărătorilor fiecare impuls de intrare reduce acest număr cu unul. Contoarele cele mai simple sunt cele binare. În Fig. 18 reprezintă contorul binar sumar și diagrama funcționării sale.

Modificați direcția contului.

După cum am menționat mai devreme, contoarele pot fi implementate pe declanșatoare. În acest caz, declanșatoarele sunt conectate în serie. Ieșirea fiecărui declanșator acționează direct asupra intrării de ceas a următorului. Pentru a implementa contorul de sumare, este necesar să conectați contorul de intrare al următorului declanșator la ieșirea inversă a celui precedent. Pentru a schimba direcția contului (realizați contorul de scădere), puteți sugera următoarele moduri:

a) să citească semnalele de ieșire ale contorului nu de la liniile drepte, ci de la ieșirile inverse ale declanșatoarelor.

Numărul format de starea ieșirilor inverse ale comutatoarelor de declanșare este legat de numărul format de starea ieșirilor directe ale declanșatorilor prin următoarea relație:

unde n este contorul de ieșire. Tabelul 26 prezintă un exemplu de relație a unui număr pe ieșirile directe cu un număr pe ieșirile inverse ale comutatoarelor declanșatoare.

Starea ieșirilor directe

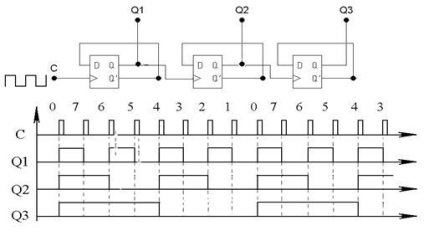

b) modifica structura legăturilor din contorul: alimentat la intrarea numărului următorului semnal de declanșare nu este inversat și o ieșire directă anterior, așa cum este prezentat în figura 19. în acest caz, schimbarea declanșează secvența de comutare.

Schimbarea factorului de conversie

Contoarele se caracterizează prin numărul de stări în timpul unei perioade (ciclu). Pentru circuitele din Fig. 18 și 19 ciclul conține N = 2 3 = 8 stări (000 la 111). Adesea numărul de state se numește coeficientul de conversie Kc, care este egal cu raportul dintre numărul de impulsuri Nc la intrare și numărul de impulsuri NQst la ieșirea celui mai mare descărcare pentru perioada:

Dacă se aplică o secvență periodică de impulsuri cu frecvența fc la intrarea contorului, frecvența fQ la ieșirea contorului de înaltă ordine al contorului va fi mai mică cu K ori: Kc = FC / FQ. Prin urmare, contoarele sunt numite și divizoare de frecvență, iar valoarea Kc este coeficientul de divizare. Pentru a crește valoarea lui Kc, este necesar să se mărească numărul de declanșatoare din lanț. Fiecare declanșator suplimentar dublează numărul de stări ale contorului și numărul de Kcs. Pentru a reduce coeficientul Kc, putem considera ieșirile declanșatorilor etapelor intermediare ca ieșiri ale contorului.

De exemplu, pentru un contor pe trei flip-flops, Kc = 8, dacă luăm ieșirea celui de-al doilea declanșator, atunci Kc = 4. În acest caz, Kc este o putere întregă de 2: 2, 4, 8, 16 etc.

Puteți implementa un contor pentru care Kc este orice număr întreg. De exemplu, pentru un contor cu trei declanșatoare, puteți face Xh de la 2 la 7, dar unul sau doi declanșatori pot fi inutili. Când folosiți cele trei declanșatoare, puteți obține Kc = 5. 7: 2 2 <Ксч<2 3. Счетчик с Ксч =5 должен иметь 5 состояний, которые в простейшем случае образуют последовательность: . Циклическое повторение этой последовательности означает, что коэффициент деления счетчика равен 5.

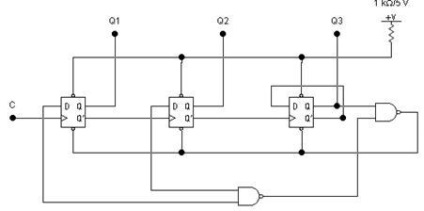

Pentru a construi un totalizator Ksch = 5 este necesar ca, după formarea ultimului dintre un contor număr de secvență nu este trecut la numărul 5, și la numărul 0. În codul binar, acest lucru înseamnă că numărul 100 pentru a trece la numărul 000, mai degrabă decât 101. Schimbarea Ordinea naturală de numărare este posibilă prin introducerea de conexiuni suplimentare între contorii declanșatori. Puteți utiliza felul următor: imediat ce contorul intră în funcțiune (în acest caz 101), acest fapt trebuie să fie identificate și să conducă la generarea ulterioară a semnalului, care s-ar traduce la contorul de stat 000. Să considerăm acest proces mai detaliat.

Faptul că contorul atinge o stare nefuncțională este descrisă printr-o ecuație logică:

.

Stările 110 și 111 sunt, de asemenea, neoperaționale și, prin urmare, sunt luate în considerare la compilarea ecuației. Dacă ieșirea circuitului logic echivalent F = 0, atunci contorul este într-una din stările de operare: 0vlv2v3v4. Odată ce ajunge la una din 5v6v7 inoperabil, format semnal F = 1. Aspectul semnalului F = 1 ar trebui să transfere contra 000 în starea inițială, prin urmare, necesar să se utilizeze acest semnal pentru a influența intrările de reglare ale declanseaza contra care au efectuat în contorul de resetare Stare Q1 = Q2 = Q3 = 0. la punerea în aplicare contor pe declanșatori cu intrări pentru setarea logică de resetare la zero declanșatoarele necesare pentru a transmite semnalul de reset R = 0. Pentru a detecta faptul că intram într-o stare nefuncțională, folosim circuitul care implementează funcția F și executată pe elementele AND-N. Pentru a face acest lucru, convertim expresia pentru funcția :.

Implementarea schematică corespunzătoare este prezentată în Figura 20.

Contorul va funcționa după cum urmează: atunci când scorul 0 - 4, totul se întâmplă în totalizare convenționale cu Ksch = 8. Semnalele de setare sunt egale cu 1, iar ordinea naturală a facturilor nu interferează. Scor apare pe frontul crescător al impulsului la C. intrare de numărare În momentul în care contorul este în starea 4 (100), următorul ceas puls contorul se transformă mai întâi într-o stare 5 (101), care imediat (cu mult înainte de sosirea următorului impuls de ceas) conduce la semnalul de resetare care este trimis către intrările de resetare a resetării declanșatorului.

Ca rezultat, contorul este resetat la 0 și așteaptă următorul impuls de ceas pentru a intra în intrarea de numărare. Un ciclu de numărare sa terminat, contorul este pregătit pentru începutul ciclului următor. Folosind un astfel de circuit de feedback pentru a reseta contorul trebuie amintit că operația de resetare durează un timp finit, prin urmare, imediat înainte de contorul este resetat la 0 la ieșirea primului bistabilului apar impulsuri scurte sau „ace“. Nu contează atunci când este conectat direct la indicatorul contorului, dar utilizarea acestei producții a contorului ca sursă de ceas poate fi unele probleme. Schema în care se elimină acest fenomen este prezentată în Fig. 21. O diferență importantă este faptul că circuitul detectează faptul de a nu cădea în stare de repaus 101, precum și faptul de a intra în starea 100 în ciclul următor generează un semnal de resetare.

Trimiteți-le prietenilor: