RS flip-flop pe poarta AND. Tabel cu adevăr, moduri de operare.

Declanșatoare. Concepte de bază RS trigger on OR - NOT. Tabel de adevăr. Mod de operare.

Exclusiv OR, exclusiv OR - NU. Tabele de adevăr. Reprezentarea grafică a elementelor.

Circuitul OR-NO constă dintr-un element OR și un invertor și negază rezultatul circuitului OR.

Elemente logice ȘI - NU, SAU - NU. Tabele de adevăr. Reprezentarea grafică a elementelor. Programul de lucru.

Circuitul NOT (invertor) implementează operația de negare.

Când cel puțin o intrare a circuitului OR este o unitate, va exista și una pe ieșire.

Circuitul OR realizează o disjuncție a două sau mai multe valori booleene.

Unitatea de la ieșirea circuitului AND va fi dacă și numai dacă există 1 unități la toate intrările. Atunci când cel puțin o intrare este zero, ieșirea va fi, de asemenea, zero.

Elementele logice ȘI, SAU, NU. Tabele de adevăr, diagrame schematice.

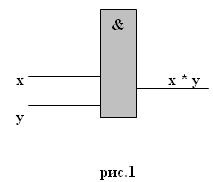

Denumirea convențională pe schemele circuitului circuitului AND cu două intrări este prezentată în figura 1 și tabelul de adevăr din tabelul 1.

Fig. 4.1. Elemente de desemnare Exclusiv OR: străin (stâng) și interior (dreapta)

Funcția Exclusiv OR înseamnă următoarele: o unitate de ieșire apare atunci când numai o intrare conține o unitate. Dacă unitățile de pe intrări sunt două sau mai multe sau dacă toate intrările au zerouri, atunci ieșirea va fi zero. Tabela de adevăr a elementului cu două intrări, exclusiv OR, este prezentată în Tabelul. 4.1. Notațiile adoptate în schemele interne și externe sunt prezentate în Fig. 4.1. Inscripția pe denumirea internă a elementului Exclusive OR "= 1" înseamnă doar că situația este evidențiată atunci când există o singură unitate la intrare.

Element exclusiv OR în seria standard un pic. Așchii Intern serie ofertă LP5 (patru de elemente cu două intrări cu 2C eliberare), LL3 și LP12, care diferă de LP5 eliberare OK. O caracteristică prea specifică este implementată de aceste elemente.

În ceea ce privește matematica, elementul OR exclusiv efectuează așa-numita operație de sumare modulo 4. Prin urmare, aceste elemente sunt numite și modulo-două adder. Așa cum am menționat deja în cursul precedent, modulul de însumare 2 este notat cu semnul plus cuprins în cerc.

Utilizarea principală a elementelor OR exclusive, urmând direct din tabelul de adevăr, constă în compararea a două semnale de intrare. În cazul în care două sau două zerouri ajung la intrările (semnalele sunt aceleași), la ieșire se formează un zero (vezi Tabelul 4.1). De obicei, în această aplicație, se aplică un nivel constant la o intrare a elementului, cu care se compară semnalul care variază în timp ce vine la cealaltă intrare. Dar, mult mai des, pentru compararea semnalelor și codurilor sunt utilizate microcircuite speciale ale comparatoarelor de cod, care vor fi luate în considerare în următoarea conferință.

Ca element adițional modulo 2, elementul exclusiv OR este folosit și în divizoare paralele și secvențiale de modulo 2, care sunt folosite pentru a calcula sumele de control ciclice. Dar, în detaliu, aceste scheme vor fi luate în considerare în prelegerile 14, 15.

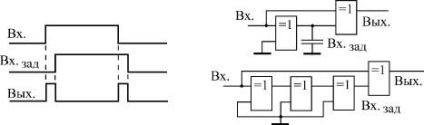

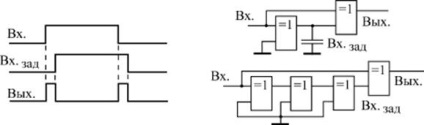

O aplicație importantă a elementelor Exclusive OR este un invertor controlat (Figura 4.2). În acest caz, una dintre intrările elementului este utilizată ca comandă, iar cealaltă intrare a elementului primește un semnal de informație. Dacă intrarea de control este una, atunci semnalul de intrare este inversat, dacă zero nu este inversat. Cel mai adesea, semnalul de control este setat de un nivel constant, determinând modul de funcționare al elementului, iar semnalul de informație este impuls. Adică elementul exclusiv OR poate schimba polaritatea semnalului de intrare sau a frontului sau poate să nu se schimbe în funcție de semnalul de comandă.

Fig. 4.2. Element Exclusiv SAU ca invertor controlat

În cazul în care există două semnale de aceeași polaritate (pozitivă sau negativă), și, astfel, sosirea lor simultană excluse elementul XOR poate fi folosit pentru a amesteca aceste semnale (Fig. 4.3). La orice polaritate a semnalelor de intrare, semnalele de ieșire ale elementului vor fi pozitive. Dacă semnalele de intrare sunt pozitive, elementul exclusiv OR va funcționa ca un element 2 sau 4 și, dacă este negativ, va înlocui elementul 2-NOR. Astfel de substituții pot fi utile în cazurile în care anumite elemente ale OR exclusivă rămân neutilizate în schemă. Adevărat, trebuie să ne amintim că întârzierea de propagare a unui semnal într-un SAU exclusiv, de obicei, este ceva mai mare (aproximativ 1,5 ori) decât întârzierea în cele mai simple elemente și, NAND, OR, NOR.

Fig. 4.3. Utilizarea elementului exclusiv-OR pentru a amesteca două semnale non-simultane

Fig. 4.4. Izolarea fronturilor semnalului de intrare utilizând elementul exclusiv OR

O altă utilizare importantă a elementului exclusiv OR este formarea impulsurilor scurte de-a lungul oricărei fețe a semnalului de intrare (Figura 4.4). În acest caz, nu contează dacă semnalul de intrare este pozitiv sau negativ, un impuls pozitiv este generat la ieșire. Semnalul de intrare este întârziat de un condensator sau de un lanț de elemente, iar semnalul original și copia întârziată sunt transmise la intrările elementului OR exclusiv. În ambele circuite, elementele de poartă cu două intrări exclusive OR în comutarea neinversivă sunt de asemenea utilizate ca elemente de întârziere (zero este folosit pentru o intrare neutilizată). Ca rezultat al acestei transformări, putem vorbi despre dublarea frecvenței semnalului de intrare, deoarece impulsurile de ieșire urmează de două ori la fel de des ca impulsurile de intrare.

Această caracteristică a elementelor exclusive OR trebuie luată în considerare atunci când ambele semnale ale elementului intră simultan pe ambele intrări ale elementului. La ieșirea elementului, pot apărea impulsuri scurte scurte pe oricare dintre fronturile semnalelor de intrare. Pentru a exclude influența lor asupra schemei ulterioare este posibilă, de exemplu, prin sincronizare similară cu cea considerată în secțiunea anterioară.

Declanșatorul RS este un declanșator cu setare separată de zero și o stare logică (cu pornire separată). Ea are două intrări de informații S și R. La intrarea S, flip-flop-ul este setat la starea Q = l (/ Q = 0), iar la intrarea R - la starea Q = 0 (/ Q = 1).

Asynchronous RS-trigger-e. Ele sunt cele mai simple declanșatoare. Ca un dispozitiv independent folosit rareori, dar reprezintă baza pentru construirea unor declanșatoare mai complexe. În funcție de structura logică, se disting RS-triggere cu intrări directe și inverse. Schemele și simbolurile lor sunt prezentate în Fig. 2.37. Declansatoarele de acest tip sunt construite pe două elemente logice: 2 NOR - declanșare cu intrări directe (. Figura 2.37, a), 2 NAND - flop cu intrare inversat (figura 2.37, b.). Ieșirea fiecăruia dintre elementele logice este conectată la una dintre intrările unui alt element, care asigură declanșatorul cu două stări stabile.

Fig. 2.37. Flip-flop-uri asincrone: a - RS-flip-flop pe elemente logice OR-NE și un simbol; b - declanșator RS pe porți NAND și un simbol.

Stările declanșatorilor sub influența unei anumite combinații de semnale de intrare sunt date în tabelele de operare (stări) (Tabelul 2.18).

Tabelul 2.18. Stările de declanșare.

Tabelele Qn (/ Qn) denotă nivelele care au fost la ieșirile flip-flop-ului înainte de aplicarea așa-numitelor nivele active la intrările sale. Active este nivelul logic care acționează la intrarea elementului logic și determină în mod unic nivelul logic al semnalului de ieșire (indiferent de nivelurile logice care acționează asupra celorlalte intrări). Pentru elementele SAU-NU pentru a lua un nivel activ un înalt nivel de - 1 și la AND-NO - nivel scăzut - niveluri O. care alimentează una dintre intrări nu modifică nivelul logic la ieșirea elementului, numit pasiv. Nivelurile Qn + 1 (/ Qn + 1) denotă nivelele logice la ieșirile flip-flop-ului după ce informația este alimentată la intrările sale. Pentru a declanșa intrări directe în timpul de alimentare a semnalului de intrare constelație S = 1, R = 0 pentru a obține ieșire Qn + 1 = 1 (/ Qn + 1 = 0). Acest mod se numește modul de înregistrare a unității logice.

Dacă este eliminat un semnal unic de la intrarea S, adică un semnal zero este setat la intrarea S, starea declanșatorului nu se va schimba. Modul S = 0, R = 0 se numește modul de stocare a informațiilor, deoarece informațiile de ieșire rămân neschimbate.

Când semnalele de intrare S = 0, R = 1 sunt introduse, declanșatorul va comuta și ieșirea va fi Qm + 1 = 0 (/ Qn + 1 = 1). Acest mod se numește modul de înregistrare zero (mod resetare). Când S = R = 1, starea bistabilului va fi incert din cauza efectului nivelelor logice semnal de informație ale ieșirilor flip-flop sunt identice (Qn + 1 = / Qn + 1 = 0) și după acțiunile lor declanșează pot lua probabil în mod egal, fie de două stabile state. Prin urmare, o astfel de combinație S = R = 1 este interzisă.

Pentru declanșatorul cu intrări inverse, modul de înregistrare al unității logice este realizat la / S = 0, / R = 1, modul de scriere zero pentru logica / S = 1, / R = 0. La / S = / R = 1, informațiile sunt stocate. Combinația semnalelor de intrare / S = / R = 0 este interzisă.

Declanșatorul RS este denumit după intrările sale. Intrarea S (Set-set English) vă permite să setați ieșirea declanșatorului Q la o singură stare. Intrarea R (resetare - resetare engleză) vă permite să resetați ieșirea declanșatorului Q (Quit - English output) la starea zero.

Pentru a implementa flip-flop-ul RS, folosim elementele logice "2N-HE". Diagrama sa schematică este prezentată în figura 2.

Figura 2. Diagrama celui mai simplu flip-flop RS pe circuitele "2N-HE". Intrările R și S sunt inverse (nivelul activ '0')

Să considerăm operația reprezentată în figura 2 RS de circuit flip-flop mai detaliat. Lăsați potențialele de intrare R și S să fie alimentate cu potențiale de unitate. Dacă ieșirea din poarta NAND superioară „NAND 2I“ Q nu este un zero logic, ieșirea de jos poarta NAND „NAND 2I“ apare unitate logică. Această unitate confirmă zero logic la ieșire Q. Când apare la zero logic ieșirea de la poarta NAND de sus „NAND 2I“ Q inițial prezentă unitate logică, ieșirea de la poarta NAND de jos „2I-NU“. Acest lucru va confirma un zero logic la Q. ieșire Aceasta este atunci când nivelurile de intrare individuale, RS flip-flop circuitul funcționează în același mod ca și circuitul invertorului.

Oferim inputului S un potențial zero. Conform tabelului cu adevărat al porții NAND, la ieșirea Q va apărea un singur potențial. Aceasta va conduce la apariția unui potențial zero la ieșirea inversă. Acum, chiar dacă potențialul zero este eliminat din intrarea S, va exista un singur potențial la ieșirea declanșatorului. Adică, am scris o unitate logică în declanșator.

În mod similar, puteți scrie o logică zero în declanșator. Pentru a face acest lucru, utilizați intrarea R. Deoarece nivelul activ la intrare a fost zero, aceste intrări sunt inverse. Noi compunem tabela de adevăr a flip-flop-ului RS. Intrările R și S din acest tabel vor utiliza linii drepte, adică un record zero, iar înregistrarea unității va fi realizată prin potențiale unice (Tabelul 1).

Tabelul 1. Tabelul de adevăr al flip-flop-ului RS.

RS flip-flop poate fi construit pe elementele logice „SAU“. Declanșatorul RS construit pe elemente logice „SAU“ este prezentată în figura 3. Singura diferență în activitatea acestui sistem față de circuitul anterior de declanșare RS va consta în faptul că descărcarea și instalarea trăgaciului va fi niveluri logice unice. Aceste caracteristici sunt legate de principiile logicii răsturnate care au considerat anterior.

Figura 3. Diagrama celui mai simplu flip-flop RS pe circuitele "OR". Intrările R și S sunt drepte (active '1')

Din moment ce RS flip-flop atunci când construirea în elemente logice „ȘI“ și „SAU“ funcționează în același mod, este o reprezentare grafică a condițională-diagramele de circuit este, de asemenea, la fel. Related imagine grafică pe RS flip-flop diagrame de circuit din figura 4.

Figura 4. Desemnarea grafică a flip-flop-ului RS

Exemplu: Activarea operației de declanșare cu o margine pozitivă și activarea acțiunii declanșatorului este negativă. Flip-flop sincronic RS.

Articole similare

Trimiteți-le prietenilor: