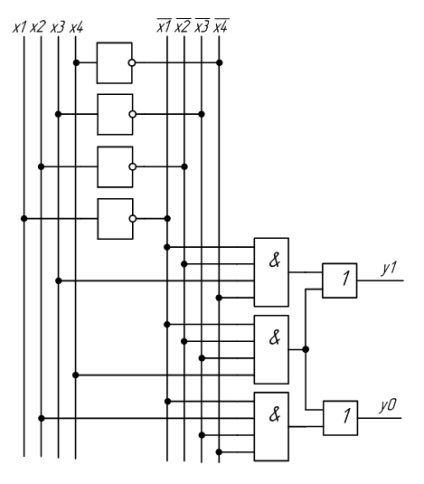

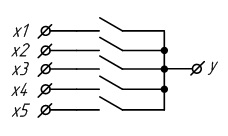

Sintetizați codificatorul. Pentru aceasta, scriem sistemul propriilor funcții:

y1 = x1 · x2 · x3 · x4 + x1 · x2 · x3 · x4

y0 = x1 · x2 · x3 · x4 + x1 · x2 · x3 · x4

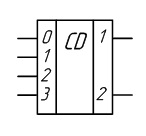

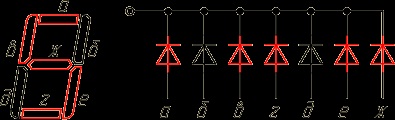

2.3 Cod de conversie pentru un indicator de șapte segmente

Convertoarele de cod cele mai utilizate sunt cunoscute pentru indicatorii digitali. De exemplu, un convertor de cod binar de poziție pe 4 biți în cifre zecimale. Există un indicator de șapte segmente și cu acesta trebuie să evidențiați zece numere.

Evident, codul binar trebuie să aibă cel puțin 4 cifre (2 ^ 4 = 16, care este mai mare de 10). Să compunem tabelul de adevăr al funcționării unui astfel de convertor.

Tabelul 2.3 - Tabela de adevăr a convertorului

Prin TI nu este dificil să se compună un sistem de funcții proprii pentru toate ieșirile, adică CDNF, minimalizați-o și elaborați o diagramă schematică.

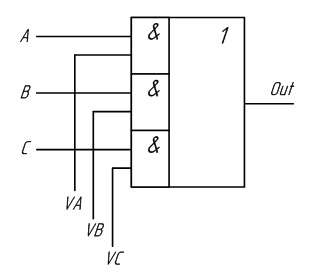

În circuitele digitale, trebuie să gestionați cheile cu niveluri logice. Prin urmare, este de dorit să alegeți un dispozitiv care să poată îndeplini funcțiile unei chei electronice cu ajutorul unui semnal digital. Să încercăm să "forțăm" să lucrăm ca o cheie electronică deja familiarizată cu elemente logice. Luați în considerare TI-ul porții AND. În acest caz, una dintre intrările gatei AND va fi considerată ca intrare de informație a cheii electronice, iar cealaltă intrare ca manager. Deoarece ambele intrări ale porții AND sunt echivalente, nu contează care este intrarea de control. Să presupunem că intrarea X este controlul, iar Y este informația. Pentru simplitatea raționamentului, împărțim TI în două părți, în funcție de nivelul semnalului logic la intrarea de control X.

Tabelul 2.4 - Tabel de adevăr

Conform tabelului de adevăr arată în mod clar că, dacă intrarea de control X a depus semnal de nivel logic zero, aplicat la intrarea Y la ieșirea Out eșuează. Când o unitate logică este introdusă la intrarea de comandă X, intrarea semnalului la intrarea Y apare la ieșirea Out. Aceasta înseamnă că poarta ȘI poate fi utilizată ca o cheie electronică. Nu contează care dintre elementul de intrare „și“ va fi utilizată ca intrare de control, și care - ca informație. Rămâne doar să combinăm ieșirile elementelor AND cu o ieșire comună. Acest lucru se face cu ajutorul „sau“ poarta logică în același mod ca și în construcția sistemului pe o tabelă de adevăr arbitrar. Versiunea rezultantă a circuitului comutatorului cu control al nivelelor logice este prezentată în Figura 2.8.

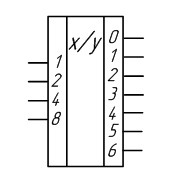

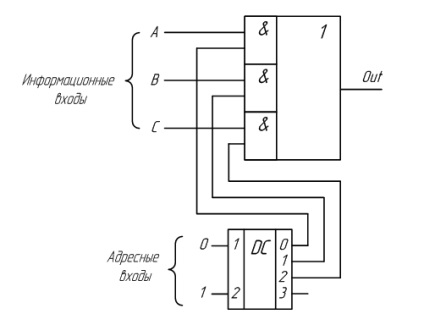

În diagramele din Figurile 2.7 și 2.8, este posibil să se includă simultan mai multe intrări pe ieșire. Cu toate acestea, aceasta duce, de obicei, la consecințe imprevizibile. În plus, sunt necesare multe intrări pentru a controla un astfel de comutator, astfel încât multiplexorul include de obicei un decodor binar, așa cum se arată în Figura 2.9. Această schemă vă permite să controlați comutarea intrărilor de informații ale multiplexorului cu ajutorul codurilor binare aplicate intrărilor sale de control. Numărul de intrări de informații din astfel de scheme este ales să fie un multiplu de putere de două.

Cu privire la caracteristicile de punere în aplicare a multiplicatorilor în limba Verilog poate fi citit în articol:

Arhitectura FPGA. Partea 2. Multiplexer

Adderul este un nod de calculator, conceput pentru a adăuga numere binare. Construcția de adaosuri binare începe de obicei cu un modulor 2 adder.

Totalizer modulo 2

Schema de însumare modulo 2 coincide cu schema care exclude "OR".

Tabelul 2.5 - Tabelul adevărului modulului 2 adder

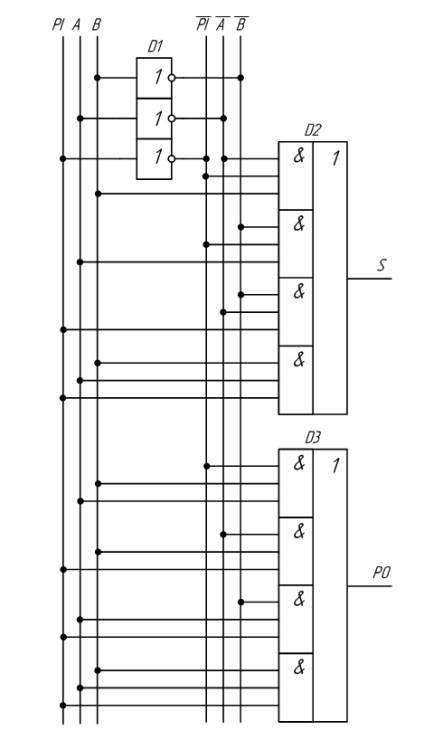

PI - intrare de transfer 1 de la cifra precedentă,

PO - ieșirea 1 a transferului la nivelul superior.

Pe baza tabelului de adevăr, scriem sistemul funcțiilor proprii pentru fiecare ieșire:

S = A · B · PI + A · B · PI + A · B · PI + A · B · PI

PO = A · B · PI + A · B · PI + A · B · PI + A · B · PI

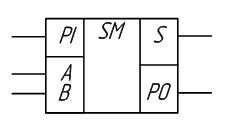

Ca rezultat, obținem schema totală a adderului (Figura 2.15).

Figura 2.16 - Imagine a unui aderent complet binar cu un singur bit pe circuite

3 Atribuirea la locul de muncă

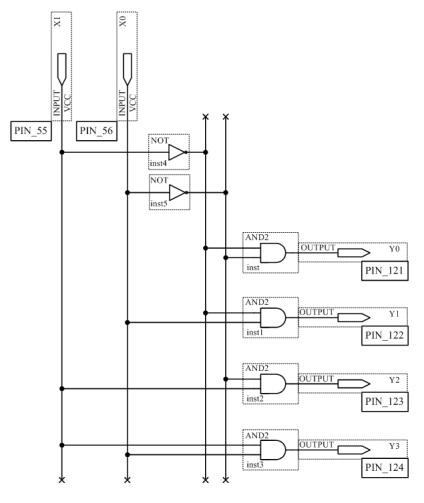

3.1 Investigați funcționarea decodorului 2 x 4

Configurați FPGA în conformitate cu Figura 3.1. Conectarea la intrările X0 și switch-uri X1 S7 și S8, iar ieșirile Y0, Y1, Y2, Y3 LED-uri LED5, LED6, LED7, LED8. Pentru aceasta, conectați intrările și ieșirile decodorului la picioarele corespunzătoare ale FPGA.

Hrănirea toate combinațiile posibile de nivele logice pe intrările X0, X1 cu ajutorul tastelor S7, S8 și observând stările indicatorului LED LED5, LED6, LED7, LED8, completați tabelul de adevăr decodor.

Tabelul 3.1 - Tabelul decodorului

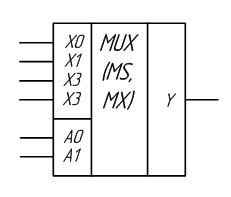

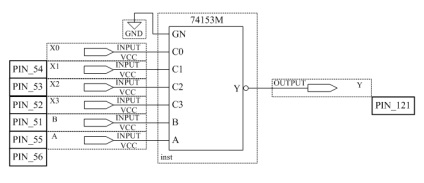

3.4 Investigați funcționarea unui multiplexor de 4x1

Configurați FPGA în conformitate cu Figura 3.4.

Tabelul 3.5 - Tabelul care descrie funcționarea multiplexorului

Numărul canalului selectat

3.5 Investigați circuitul de împărțire

Configurați FPGA în conformitate cu Figura 3.5. Aici Pin. Pout, respectiv, intrarea și ieșirea unității de transfer, A și B sunt summands, iar S este suma.

Figura 3.5 - Schema agregatului

Completați tabelul cu adevărat al numărătorului (tabelul 3.6).

Tabelul 2.7 - Tabelul de adevăr al agregatului total

- Scopul lucrării.

- Scheme de investigare a decodorului, codificatorului, convertorului de cod pentru indicator de șapte segmente, multiplexor, adder.

- Tabele de adevăr pentru fiecare schemă.

- Concluzii pentru fiecare sarcină.

5 Încercați întrebări

- Cum funcționează decodorul?

- Cum de a sintetiza un decodor cu o adâncime de biți arbitrară?

- Cum funcționează codificatorul?

- Imaginează tabela de adevăr a codorului.

- Cum funcționează convertorul de cod pentru indicatorul de șapte segmente?

- Cum este aranjat indicatorul cu șapte segmente?

- Cum funcționează multiplexorul?

- Cum a fost studiul multiplexorului în laborator?

- Cum functioneaza adderul?

- Imaginează tabela de adevăr a codorului.

- Ce este o unitate de transport?

Ortografie în text:

Articole similare

Trimiteți-le prietenilor: