Programul pentru vhdl există deja, acum vă voi spune ce să faceți cu el.

La pornire, programul sugerează crearea unui nou proiect sau deschiderea unui proiect existent.

selectați "Creați un nou proiect", dacă ați introdus deja programul, atunci

Fișier-> Expertul pentru proiecte noi ...

Nu cred că veți vedea ceva nou: alegerea catalogului și numele proiectului, adăugarea fișierelor în proiect, alegerea chipului, finisarea.

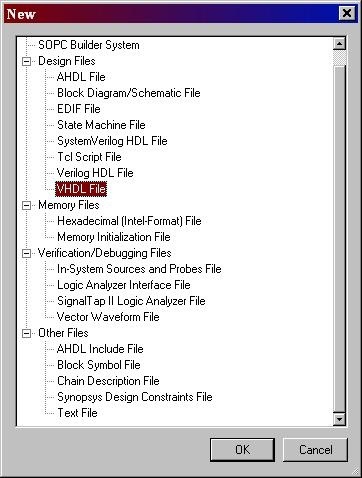

Acum trebuie să creați un fișier (bazat pe articolul "Ce este VHDL." Cel mai simplu exemplu de a crea un element logic într-un FPGA) este de a crea un fișier vhdl

File-> New-> Fișier VHDL

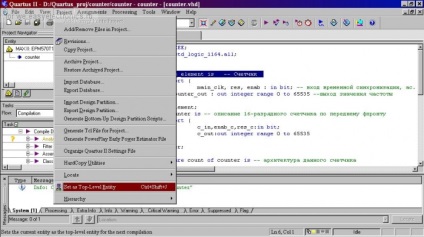

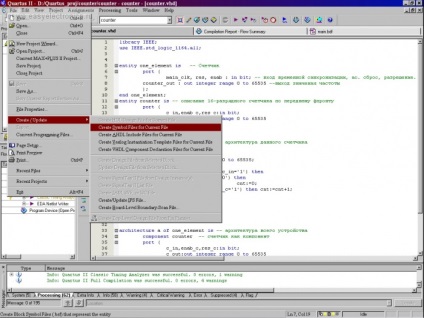

Copiem tot codul, îl salvăm. Acum îi spunem programului că acesta este fișierul principal al proiectului

Proiect-> Stabilit ca entitate de nivel superior

(fără acest lucru nu se întâmplă nimic).

Este posibil să se compileze.

Prelucrare-> Start compilare (Ctrl + L)

sau un triunghi purpuriu în partea de sus a panoului.

Este afișat un raport de compilare, dacă totul este bine, mergeți mai departe.

Înainte de firmware, trebuie să atribuiți o potrivire între semnalele de intrare și ieșire din proiect și pinii cipului. Plecăm

Assignments-> Pins

Mai jos puteți vedea numele semnalelor noastre. În câmpul Locație, selectați pur și simplu știftul dorit sau faceți dublu clic pe pin (unde este imaginea chip) și selectați numele dorit.

În FPGA toți pinii sunt egali, pot fi fie intrări sau ieșiri, fie bidirecționale. Unele concluzii pot fi o sursă de ceasuri globale, resetare globală sau globală. În proiectul nostru, există toate aceste tipuri de semnale nu este cu siguranță necesar pentru a le conecta la aceste ace, dar în proiecte mari, în cazul în care un semnal de ceas merge la o mulțime de module, acesta va fi mai eficient, deoarece acestea sunt fizic bine construite în interiorul cip. De asemenea, în funcție de cip specifică poate fi selectată capacitate de încărcare de ieșire, rezistor pull-up sau pentru a conecta o diodă de protecție.

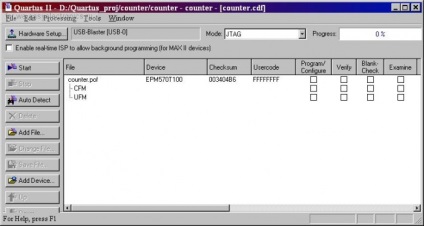

După asignarea pinului, puteți începe programarea

Instrumente-> Programator

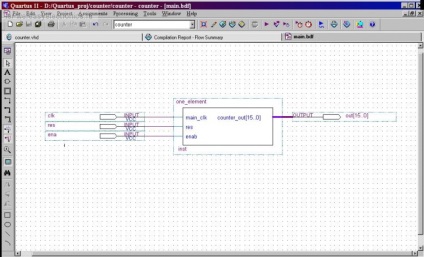

Atunci când un proiect constă din mai multe fișiere (și acesta este cel mai adesea), atunci este convenabil ca fișierul principal să fie o descriere schematică. crea

File-> New-> Diagramă bloc / fișier schematic

Salvați-l, numiți-l principal.

Pentru a adăuga fișierul vhdl acolo, trebuie să creați un fișier de simboluri din acesta. Pentru aceasta, selectați fișierul vhdl, faceți clic pe

Fișier-> Creare / Actualizare-> Creare fișier simbol pentru fișierul curent

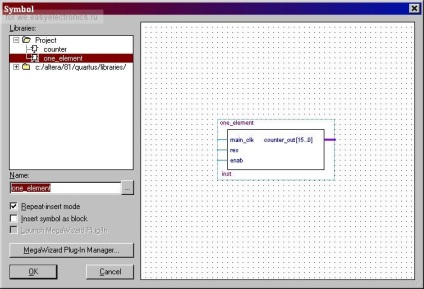

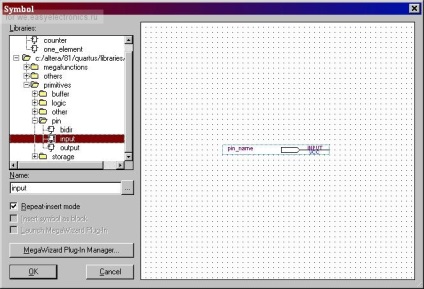

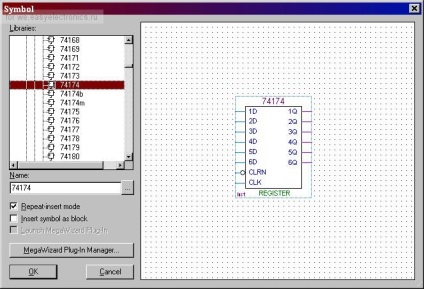

Ne intoarcem la main.bdf, faceti clic pe Instrumentul Symbol (butonul sub forma unei poarta AND).

Programul a creat fișiere cu 2 caractere, deoarece în vhdl două entități. De fapt, ceea ce am descris în entitatea pe care o vedem în imaginea acestui fișier simbol, o cutie neagră care are intrări și ieșiri, dar ceea ce se întâmplă în el este descris în arhitectură.

Acum adăugăm ace, dă-le un nume de semnificație.

Ar trebui să obțineți ceva de genul:

Aici puteți adăuga diferite piese interesante, cum ar fi chips-uri logice standard sau diverse adders, multiplexoare și așa mai departe.

De asemenea, în funcție de chipul folosit, "umplutura" sub formă de memorie sau ca în familia MAX II, generatorul încorporat la 5 MHz. Totul este adăugat și conectat prin fire, iar în chip va fi și fizic conectat.

Salvați fișierul, efectuați-l din nou

Proiect-> Stabilit ca entitate de nivel superior

Acum remarcile mele și finalizarea proiectului.

Aici, 2 entitate va fi superfluă, deoarece într-un fișier schematic este posibilă conectarea tuturor blocurilor în mod obișnuit și pornirea unui semnal oriunde.

De asemenea, nu este nevoie să conectați biblioteca, deoarece nu este utilizată (descrie semnale de tip std_logic).

Dosarul nostru este simplificat

acum voi adăuga 5 cenți la codul meu

scuze

Din punct de vedere istoric, am descris crearea proiectului în Quartus pentru primul articol despre vhdl, deși ar fi fost mai bine pentru al doilea. Dar din moment ce am avut comentarii cu privire la acest articol și, de asemenea, am vrut să arăt Ultrin cum să creeze un proiect în Quartus, am decis să nu fac nimic.

În general, tema FPGA devine populară, dar în special pentru mine. Nu am citit încă toate articolele, dar încă nu decid ce producător să se oprească - Altera sau Xilinx. În orice caz, sunt extrem de bucuroasă că această comunitate a apărut, iar oamenii se prezintă articole pe tema FPGA-urilor, iar apoi este oarecum trist să începem cu literatura și fișele tehnice străine.

PS. În paralel, încerc să stăpânesc AVR-ul. Nicho so)))))))))

Zzy. Apel la cei care știu și pot: Voi fi foarte recunoscător pentru tine (probabil nu numai mine), dacă continuați să discutați despre acest subiect interesant cu același entuziasm

În fosta Uniune Sovietică într-un fel de produse Alterovskaya sunt mai populare (IMHO, probabil în faptul că există centre oficiale Altera), dar și din străinătate, mai ales în Japonia, iar coreenii din Europa este foarte comun cu evoluțiile de la Xilinx. În opinia mea, există mai multe materiale în limba rusă sub alter și este mai ușor de învățat.

Ei bine, deja jenat. Uită-te la prețurile în terraelectronics la fel.

Și prin sabzh: asta este logica bună în contrast cu controlorul - este:

- Bineînțeles, totul este paralealizat (și acesta este principalul lucru!). Gândiți-vă la ceva, lei în UART, citiți de la SPI - toate în același timp, dacă numai memoria a fost în timp (bine, dacă este necesar).

- Câteva interfețe? Adăugați cel puțin câte, ce ar trebui să fie pe o singură piatră.

Există, desigur, lucruri pentru care logica, IMHO, nu este un lucru foarte potrivit: de exemplu, suport pentru FAT, stack TCP / IP ... și tot ce îmi amintesc este :)

De asemenea, nu trebuie să vă ocupați de gunoi și să încercați să strângeți o logică în logică, de exemplu, alter Nios al II-lea. Este inutil, e mai bine sa il pregatesti, inca va castiga in viteza, iar hemoragia va fi mult mai mica.

Ei bine, dacă există resurse neexploatate, atunci este mai bine să-i chinuiți și mai mult decât să vă puneți în afară. În general, multe lucruri care se produc pe MCU / procesor pot fi adesea înlocuite cu o mașină digitală sofisticată automată.

Pentru începători, voi recomanda o serie bună de articole despre Quartus I. Există, de asemenea, compilație și scopul porturilor, modelarea și TimeKvest.

EasyEDA: Free Cloud CAD

live acum

Articole similare

Trimiteți-le prietenilor: