ModelSim Simulator

Vreau să vă spun câteva lucruri despre simularea proiectelor digitale. Da, da. Acest subiect a fost deja ridicat de mai multe ori și, desigur, acesta este un subiect inepuizabil. Am scris deja despre simulare folosind Quartus II versiunea 9. Dar în ultima versiune de Quartus II v10 acest "nativ" simulator Alter nu mai este acolo. Pentru a spune adevărul, am fost supărat. Pentru proiectele mici, acest simulator este suficient. Apoi am scris un articol despre simulatorul iverilog - este un simplu simulator open source - lucru destul de decent. Și acum vreau să vorbesc pe scurt despre programul ModelSim:

Voi vorbi despre una dintre versiunile sale, și anume ModelSim Altera Starter Edition.

Acolo veți vedea un tabel cu caracteristicile comparative ale diferitelor versiuni ale ModelSim:

Alegem versiunea pentru începători - este gratuită, nu necesită o licență, poate fi folosită pe proiecte mici de până la 10.000 de linii de cod. Cred că e suficient pentru noi. Faceți clic pe linkul Descărcare. Am ales versiunea pentru Windows. Dimensiunea fișierului care trebuie descărcat este de 586 MB. Acest lucru nu este mic, dar nu prea multe în prezent. În general, mă agită și instalez ..

Vreau acum să simulez același exemplu pe care deja am încercat să-l simt cu iverilog. Acestea sunt două fișiere counter.v și tcounter.v - acestea sunt localizate în folderul meu c: \ altera \ 10.0 \ projects \ first.

Conținutul acestor fișiere este astfel:

counter.v este un contor cu posibilitatea încărcării paralele. Dacă semnalul wr este activ în momentul în care se află clk frontal. atunci numărul din magia magistralei de intrare va fi scris la contor. În caz contrar, valoarea contorului va crește cu câte o față în față a clk.

contor de module (

Resetarea firului de intrare,

sârmă de intrare clk,

sârmă de intrare [7: 0]

cablu de intrare wr,

ieșire reg [7: 0] date

);

mereu @ (posedge clk sau posedge reset)

dacă (resetați)

date <= 8'h00;

altfel

dacă (wr)

date <= wdata;

altfel

date <= data + 8'h01;

Și aici este - vcounter.v - "testbench" pentru contorul meu. Acest program este folosit pentru a verifica funcționarea corectă a modulului de contorizare.

`calendarul 1ns / 100ps

modul test_counter;

reg reset, clk, wr;

reg [7: 0];

sârmă [7: 0] date_cnt;

contra counter_inst (resetare, clk, wdata, wr, data_cnt);

inițială

începe

clk = 0;

resetare = 0;

wdata = 8'h00;

wr = 1'b0;

# 50 resetare = 1;

# 4 resetare = 0;

# 50;

@ (posedge clk)

# 0

începe

wdata = 8'h55;

wr = 1'b1;

capăt

@ (posedge clk)

# 0

începe

wdata = 8'h00;

wr = 1'b0;

capăt

capăt

inițială

începe

# 400 $ finisaj;

capăt

inițială

începe

$ dumpfile ("out.vcd");

$ dumpvars (0, test_counter);

$ dumpvars (0, contra_inst);

capăt

inițială

$ monitor ($ stime, resetare, clk, wdata, wr. data_cnt);

Iată fișierele pe care le voi încerca să le folosesc pentru a demonstra munca lui ModelSim.

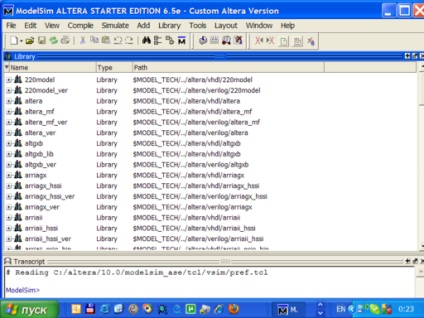

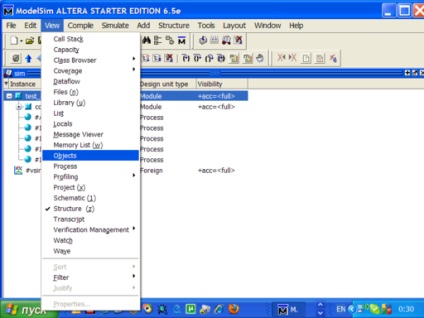

Când rulați programul ModelSim, vedem ceva asemănător cu acest ecran (faceți clic pe imagine pentru ao vedea mai mare):

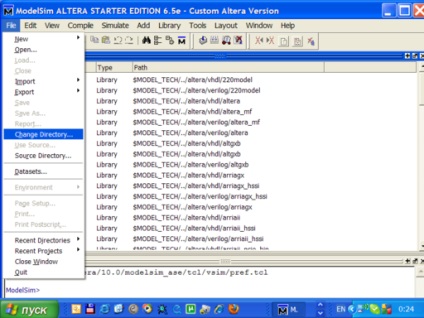

Primul lucru pe care trebuie să-l facem este să mergeți la dosarul de lucru. Pentru aceasta, selectați elementul de meniu File / Change Directory.

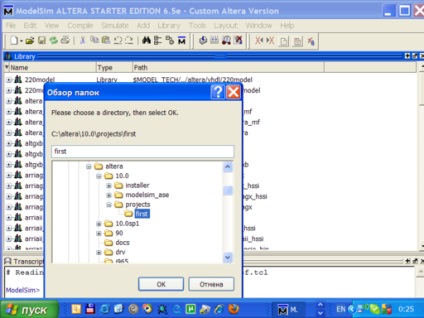

În dialogul care se deschide, specificăm calea spre proiectul nostru:

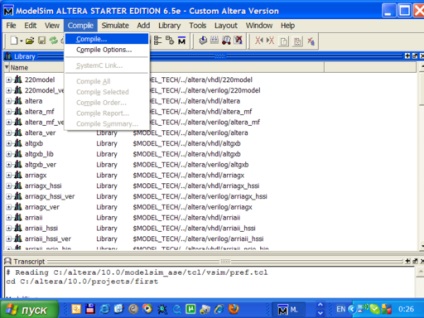

După selectarea dosarului, trebuie să compilați proiectul în bibliotecă. Selectați elementul de meniu Compilați / Compilați.

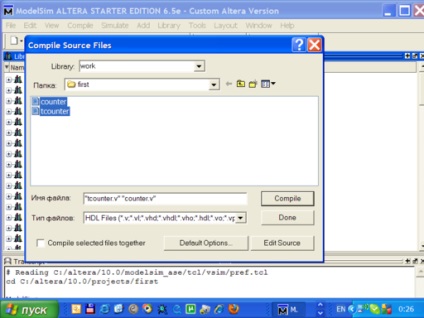

Aici trebuie să selectați toate fișierele proiectului nostru. Dialogul vă permite să selectați mai multe fișiere în același timp.

Alegeți fișiere - apăsați butonul Compilare.

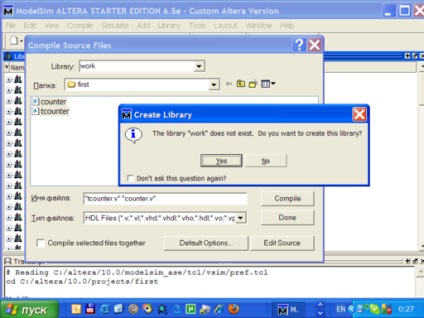

ModelSim solicită crearea bibliotecii. Numele implicit este locul de muncă. Ei bine, să se întâmple asta. Noi răspundem Da. După compilație în fereastra Transcript, verificați dacă există erori în fișierele sursă.

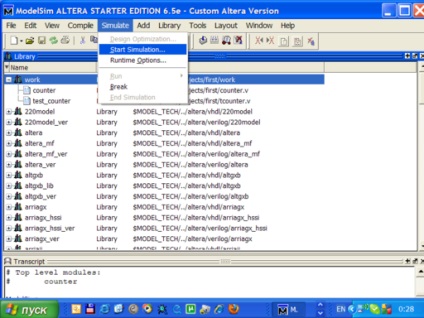

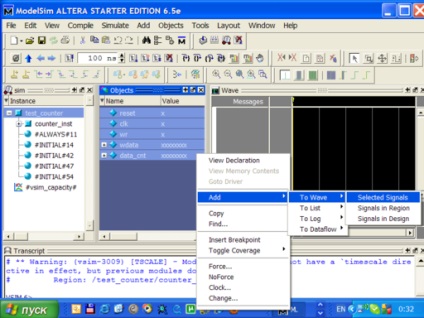

Rețineți că o nouă bibliotecă de lucrări a fost adăugată în fereastra Bibliotecă. ar trebui să fie așa. Acum, selectați elementul de meniu Simulare / Pornire simulare.

Acum, să vedem ce avem în simulare. Facem câțiva pași de simulare înainte folosind elementul de meniu Simulate \ Run \ Run100.

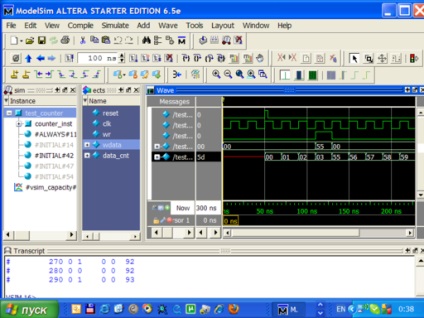

Iată rezultatul simulării:

Rețineți că atît ieșirea textului din fereastra Transcriere, cât și semnalele din fereastra Wave sunt exact aceleași ca în cazul simulării folosind icarus-verilog cu sursă deschisă.

Ei bine, și - sub formă de semnale, vedem că contorul nostru funcționează corect - așa cum am intenționat!

Cineva ajută să instaleze Modelsim pe ubuntu. La lansare emite "./vish: eroare în timpul încărcării bibliotecilor partajate: libXft.so.2: nu se poate deschide fișierul obiect partajat: Nici un astfel de fișier sau director".

încercați să instalați biblioteci suplimentare sudo apt-get install libxft2

Cineva ajută să instaleze Modelsim pe ubuntu. La lansare emite "./vish: eroare în timpul încărcării bibliotecilor partajate: libXft.so.2: nu se poate deschide fișierul obiect partajat: Nici un astfel de fișier sau director".

Citez pe Molin Dmitry:

Aceeași problemă ca și Vadim și Ia.

Modelsim emite linii drepte, în timp ce face totul, așa cum este scris în articol. De asemenea, am scris propriile mele programe și chiar am încercat să mă uit la funcționarea elementelor din bibliotecile standard, dar rezultatul este același.

A fost la fel, a fost stabilit după cum urmează: atunci când Simulate \ Start Simulation trebuie să selectați un singur fișier testbench, am ales amândoi - există linii drepte. Pentru a face impulsurile similare cu cele din capturile de ecran, puteți reduce scara graficului (faceți clic dreapta - apoi găsiți).

Înțeles - dacă specificați ambele module (testate și testbench) într-un fișier, atunci ModelSim nu va putea afișa rezultatele simulării. În general, este posibil acest lucru?

Utilizăm tipul de fir pentru a simula semnalul de ieșire, mai degrabă decât reg numai pentru a nu "stoca" starea semnalului în registru și pentru a evita costurile hardware?

Domnilor, niciodată nu știți cine va răspunde la citirea articolului, au apărut câteva întrebări stupide:

1) Este posibil să se scrie un testbench în același fișier ca modul testat, doar testbench va fi pus în aplicare ca un alt modul? (Știu că a fost insolent, deoarece poate fi navigat cu ușurință, dar câți nu este o povară)

2) De ce a fost creat (a fost declarat) semnalul de sârmă [7: 0] data_cnt în testbench?

Am înțeles corect:

contra counter_inst (re setat, clk, wdata, wr, data_cnt); - Prin această linie, creăm o instanță a modulului de contor și înlocuim registrul de date de ieșire cu semnalul data_cnt? și care este semnificația acestei acțiuni, de ce nu a putut fi înlocuită de un semnal cu aceleași date de nume sau chiar cu un registru de date, ca în modulul testat? Poate registrul să fie o ieșire testbench la toate, sau este doar întotdeauna un semnal, ca ieșire?

Aceeași problemă ca și Vadim și Ia.

Modelsim emite linii drepte, în timp ce face totul, așa cum este scris în articol. De asemenea, am scris propriile mele programe și chiar am încercat să mă uit la funcționarea elementelor din bibliotecile standard, dar rezultatul este același.

A fost la fel, a fost stabilit după cum urmează: atunci când Simulate \ Start Simulation trebuie să selectați un singur fișier testbench, am ales amândoi - există linii drepte. Pentru a face impulsurile similare cu cele din capturile de ecran, puteți reduce scara graficului (faceți clic dreapta - apoi găsiți).

Articole similare

-

Scrierea și rularea unui script pentru a simula codul verilog în modelsim

-

Incredibil de complex și încă amuzant tracker și atletism atletism qwop cuceri Google Play -

Trimiteți-le prietenilor: