2.5.3. JK Triggers

JK-trigger-ele sunt împărțite în universale și combinate. Flip-flopul universal JK are două intrări de informații J și K. La intrarea J, flip-flop-ul este setat la starea Q = 1, / Q = 0, iar la intrarea K - în starea Q = 0, / Q = 1.

Flip-flopul JK diferă de flip-flop-ul RS, în primul rând prin faptul că elimină incertitudinea care apare în flip-flop RS cu o anumită combinație de semnale de intrare.

Utilitatea JK-flip-flop-ului este că poate să efectueze funcțiile de flip-flops RS, T și D.

JK-declanșatorul combinat diferă de cel universal prin prezența altor intrări asincrone S și R pentru presetarea declanșatorului la o anumită stare (logică 1 sau 0).

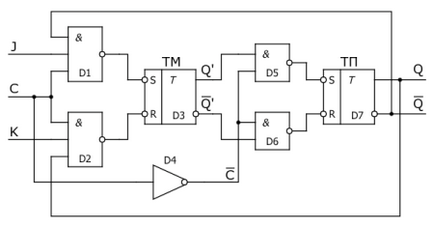

Cel mai simplu JK-flip-flop pot fi obținute de la sincron RS-declanșare cu control dinamic, dacă introducem feedback suplimentar de la ieșirile la intrările bistabilului, care poate elimina incertitudinea din tabelul de stare (Fig. 2.50.a).

Fig. 2.50.a. Conversia flip-flop-ului sincronal la JK-flip-flop;

Dacă intrările J și K dau nivelul de unitate logică, obținem un flip-flop T, care este comutat de fiecare impuls de intrare (Figura 2.50, b).

Fig. 2.50.b. Transformarea JK-flip-flop-ului într-un flip-flop T;

În Fig. 2.50.c sunt date simbolul declanșatorului JK și tabelul de stări. Cu semnalele de intrare J = K = 0, starea declanșatorului nu se schimbă, deoarece tensiunea joasă la o intrare a elementului AND-NO anulează semnalul de la celelalte intrări și menține semnalul de ieșire în starea logică curentă.

Fig. 2.50.v. simbol al JK-flip-flop-ului

Tabelul de stat al JK-flip-flop-ului

Dacă aplicați nivelele opuse față de intrările J și K, atunci când scaderea de tensiune este aplicată la intrarea C, ieșirile declanșatorului JK sunt setate la aceleași stări. Atunci când tensiunile mari și ridicate sunt aplicate simultan la intrările J și K, declanșatorul este comutat la opusul stării anterioare dacă apare o scădere de tensiune la intrarea de sincronizare C.

Controlul impulsului ceasului complet aplicat la intrarea C este folosit pentru declanșatoarele în două trepte (Figura 2.50.d).

Fig. 2.50.g. în două trepte JK-trigger;

Un astfel de declanșator are și feedback de la ieșiri la intrări, eliminând starea nedeterminată a declanșatorului.

Fig. 2.50.d. JK-trigger în două trepte pe elementele logice AND-NOT

cu un circuit de comandă simetric al declanșatorului de a doua treaptă;

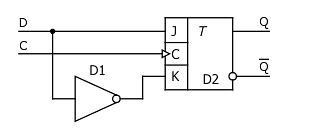

Din flip-flopul JK este posibil să se obțină un flip-flop D dacă intrarea K este conectată la intrarea J printr-un invertor suplimentar (Fig.2.50, d).

Fig. 2.50.e. Circuitul conversiei JK-flip-flop în flip-flop D

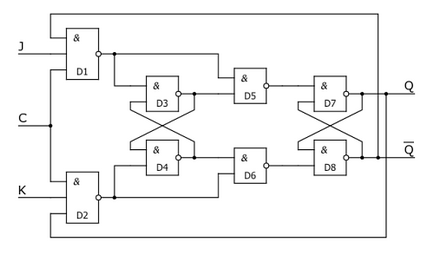

Cipul TB1 (Figura 2.51) este un declanșator universal în două trepte JK.

Fig. 2,51. JK-trigger combinat - structura chipului, simbolul și pinoul chipului TV1.

Declanșatorul are intrări asincrone inverse ale / S și resetare / R, adică cu nivel scăzut activ. Dacă aceste intrări se aplică niveluri opuse (reduse - 0 și high - 1), intrările J, K și C nu acționează și starea ieșirilor Q și / Q de declanșare definite semnale pe intrările / S și / R, masa de stat (Tabelul 2.27. ).

Tabelul 2.27. Stările de declanșare TB1

Atunci când tensiunile de nivel înalt sunt aplicate intrărilor / S și / R, informațiile pot fi încărcate în flip-flop de la intrările J și K sau stocate (vezi tabelul de stare). Fiecare dintre intrările J și K este echipată cu un element logic 3I, adică cipul TV1 are trei intrări J și trei intrări K. Intrare sincronizare C dinamic invers. două trepte stare comutator de declanșare în creștere și care se încadrează marginile impulsului pozitiv aplicat la intrare de ceas C. Informații cu J și intrările K este încărcat în prima etapă flip-flop (elemente DD1.3 și DD1.4), atunci când tensiunea schimbă de intrare C de la mici la mari (pentru din față) și transferat pe declanșatorul celei de-a doua etape de-a lungul marginii negative a impulsului de sincronizare (în decădere). Semnalele de intrare J și K nu trebuie să se modifice dacă există o tensiune ridicată pe intrare / C Picioare ieșirile Q și / Q sunt nedefinite dacă intrările / S și / R se aplică simultan tensiune de nivel scăzut, adică. E. O combinație de semnale / S = / R = 0 este interzisă.

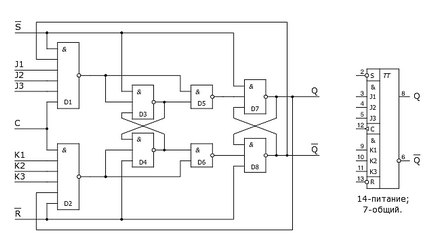

Cipurile TV6 și TV9, TV10 și TB11 au fiecare câte două jgheaburi JK cu un pin de putere comun (Figura 2.52).

Fig. 2,52. Structura, denumirea convențională și pinui de microcircuite TV6, TV9;

Fig. 2.52a. Structura, simbolul și pinoul chipului TV10;

Cu intrarea de ceas de toate flip-flops invers dinamic, astfel încât datele de intrare J și K sunt transferate la ieșirile Q și / Q a pulsului diferential negativ S. Când pulsul la intrare C merge de la mare la mic, semnalele de la intrările J și K nu trebuie modificate . Informațiile de la intrările J și K ar trebui încărcate în declanșator atunci când intrarea C are o tensiune ridicată.

Declanșatoarele cipului TV6 nu au o intrare prestabilită / S, deci în tabelul de stare (declanșator combinat JK), prima linie (setarea asincronă 1) trebuie exclusă. Dacă se aplică tensiune joasă la intrarea / R, intrările J, K și C nu funcționează.

Flip-flops-urile cipului TV10 nu au o intrare / R de pre-resetare, deci în tabela de stare a declanșatorului combinat JK este necesar să excludem a doua linie (resetare asincronă 0).

Pentru chips-urile TV6 și TV10 în tabelul de stare, a treia linie nu are sens, deoarece acestea au doar o intrare asincronă (fie / S sau / R). Declanșatoarele cipului TV11, spre deosebire de declanșatoarele cipului TV9, au două circuite comune de comandă: intrarea de sincronizare / C și intrarea de resetare asincronă / R (Figura 2.53).

Fig. 2.53. Simbol și pinout al cipului TV11

Cipurile TV14 și TV15 conțin două jgheaburi combinate JK, care sunt declanșate de o diferență pozitivă în impulsul de sincronizare, adică intrarea C este dinamică directă. Caracteristica distinctivă a acestor declanșează cipuri este că a doua intrare de date / K - (. Figura 2.54) invers, deci este foarte ușor JK-bistabile sunt convertite la D-flip-flops.

Fig. 2.54. Structura TV15, legendă și pinout TV14 și TB15

Starea acestor declanșatoare este prezentată în Tabelul. 2.28.

Tabelul 2.28. Declanșatorul declară TB15

Trimiteți-le prietenilor: