Pentru a implementa un dispozitiv de combinație digitală într-o tabelă cu adevărat folosind poarta OR (CKNF), este suficient să luați în considerare numai acele linii de masă a adevărului care conțin semnul logic "0" în semnalul de ieșire. Liniile care conțin logica "1" în ieșirea expresiei logice și, în consecință, diagrama schematică a dispozitivului digital, nu participă. Fiecare linie care conține semnalul "0" logic în semnalul de ieșire este realizată de circuitul logic "OR" cu numărul de intrări, care coincide cu numărul de semnale de intrare din tabelul de adevăr.

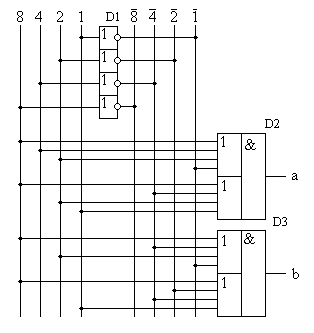

Pentru a construi un circuit care implementează semnalul Out0, este suficient să se ia în considerare liniile indicate în italice. În tabelul de adevăr în discuție, există doar două linii care conțin un logic zero în semnalul de ieșire a, prin urmare formula SKNF va conține două sume de semnale de intrare:

Semnalele de intrare sunt descrise în tabelul de adevăr al logicii zero sunt introduse la acest circuit direct, iar semnalele de intrare descrise în tabelul de adevăr al unității logice sunt furnizate elementul logic „OR“ prin invertoare. Combinarea semnalelor de la ieșirile circuitelor "OR" care implementează liniile individuale ale tabelului de adevăr se face folosind diagrama circuite AND. Numărul de intrări în circuitul AND este determinat de numărul de rânduri din tabelul de adevăr în care semnalul logic este prezent în semnalul de ieșire.

Formula rezultată din circuitul din figura 9 este implementată prin cip D2.

Pentru a construi un circuit care realizează semnalul b, este suficient să luați în considerare liniile cu caractere aldine. Aceste linii din diagrama din figura sunt implementate de cipul D3. Principiul construirii acestei scheme nu diferă de exemplul considerat mai sus. În tabelul de adevăr, există doar două linii care conțin zero în semnalul de ieșire b, deci în formula CSCF a ieșirii b vor fi două sume de semnale de intrare:

Circuite digitale combinate. Decodor. Decodificatorul zecimal

Decodoarele (decodoare) vă permit să convertiți un tip de cod binar la altul. De exemplu, convertiți un cod binar pozițional în octal sau hexazecimal liniar. Transformarea se face în conformitate cu regulile descrise în tabelele de adevăr, astfel încât construcția decodoarelor nu prezintă dificultăți.

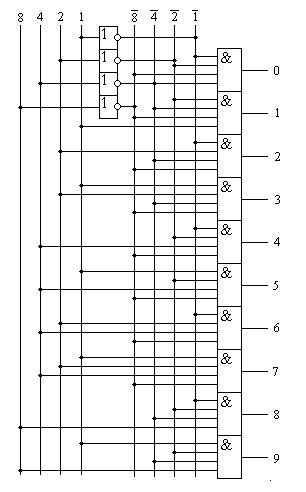

Luați în considerare un exemplu de construire a unui decodor (decodor) de la codul binar la cel zecimal. Codul zecimal este de obicei afișat cu un bit pe cifră zecimală. Acesta este un exemplu clasic, ilustrând faptul că nu numai codurile binare sunt descrise prin zerouri și altele. Codul zecimal are zece cifre, deci sunt necesare 10 ieșiri de decodor pentru afișarea unei zecimale. O cifră zecimală este semnalizată în jurul fiecărei cifre a codului zecimal, care este afișată de unitatea logică din această categorie. Semnalul de la acești pini ai decodorului poate fi alimentat la indicatorul zecimal. În cel mai simplu caz, puteți să semnați pur și simplu cifra afișată pe LED. La intrarea decodorului, codul binar este scris în conformitate cu regulile sistemului de numere binare. Decodificatorul zecimal al tabelului de adevăr este prezentat în tabelul 1.

Tabelul 1. Decodificatorul zecimal al tabelului de adevăr.

În conformitate cu principiile schemei de construcție pentru tabelul de adevăr arbitrar obține circuitul decodor care implementează tabelul de adevăr date în tabelul 1. Această schemă este prezentată în Figura 1.

După cum puteți vedea în această diagramă, pentru a pune în aplicare fiecare linie a tabelului de adevăr, a fost necesară schema "4I". Schema "OR" nu a fost necesară, deoarece în tabelul de adevăr există o singură unitate la fiecare ieșire.

Decodoarele sunt disponibile ca jetoane separate sau utilizate în alte microcircuite. În prezent, decimale sau octale decodoare sunt utilizate în principal ca parte a altor circuite, cum ar fi multiplexoare, demultiplexoare, ROM sau RAM.

Related simbol grafic cip decodor pe diagramele de circuit prezentate în figura 2. Această figură prezintă desemnarea decodorului BCD, al cărui circuit diagramă schematică internă totală este prezentată în figura 1.

Pentru a continua descărcarea, trebuie să colectați imaginea:

Articole similare

-

Casă de casă - case de cabane, case combinate în stilul unei cabane sub cheie

-

Rețeaua de lumini pe acoperiș, testul și diagrama, exemplele video și foto

-

Îngerul schemei de pâslă, clasa de masterat cu descriere detaliată, lecții video

Trimiteți-le prietenilor: