Pentru a înțelege pe deplin interfața cu două fire (TWI). scriem de la zero in procedura AVR STUDIO de initializare, citire si scriere. Ne oprim la fiecare pas în detaliu și înțelegem. Atunci vom simula totul în Proteus.

Modul hardware TWI și protocolul I2C

Microcontrolerele seriei MEGA includ modulul TWI, cu care vom lucra cu magistrala I2C. Modulul TWI este în esență un intermediar între programul nostru și dispozitivul conectat (de exemplu, memoria E2ROM I2C).

Structura modulului TWI în microcontrolerele AVR

Autobuzul I2C este format din două fire:

- SCL (Linia ceasului serial) - linia de transmisie serială a impulsurilor de ceas.

- SDA (linie serială de date) - o linie de transmisie de date în serie.

În acest autobuz, putem conecta simultan până la 128 de jetoane.

Conexiuni la magistrala TWI

După cum se poate vedea în diagrama bloc, TWI constă din patru blocuri. Inițial, va trebui să configuram Generatorul de viteză a legăturii și vom uita imediat acest lucru. Lucrarea principală este cu unitatea de control.

Deci, sarcina noastră este acum de a face față registrelor incluse în generatorul de viteză de comunicație și unitatea de comandă:

Registrul vitezei de comunicație TWBR

Registrul de gestionare TWCR

Registrul de stare TWSR

Registrul de date TWDR

Și toate, având înțeles doar cu 4 registre, putem lucra pe deplin cu memoria externă EEPROM și, în general, putem schimba datele despre I2C cu orice alt dispozitiv.

Generator de viteză de comunicație și registru de viteză de comunicație TWBR

Blocul generatorului de viteză de comunicație controlează linia SCL, și anume perioada ceasului. Linia SCL poate fi controlată numai de comandant. Perioada SCL este controlată prin setarea registrului de viteză de comunicație TWI (TWBR) și a bitului prescaler în registrul de stare TWI (TWSR).

Frecventa SCL este generata folosind urmatoarea formula:

- TWBR este valoarea din registrul ratei de comunicații TWI;

- TWPS este valoarea biților de prescaler din registrul de stare TWI (TWSR).

- Ftspu - frecvența ceasului master

- FSCL este frecvența ceasului liniei SCL

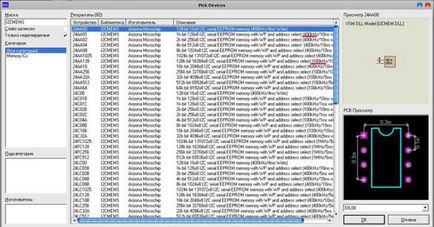

Configurația TWBR este necesară, deoarece Cipul slave este instruit să facă schimb de date la o anumită frecvență. De exemplu, în Proteus, intrați în căutarea I2CMEM, veți vedea o abundență de cipuri de memorie, în principiu au frecvențe de 100 și 400Khz.

Ei bine, substituind în formula frecvențele FCPU și FSCL. putem găsi valoarea optimă pentru registrul TWBR.

TWPS - Acesta este un număr de 2 biți [TWPS1: TWPS0], primul bit - un TWPS0 de descărcare de gestiune, al doilea - TWPS1 TWSR în registrul de stare. Atribuirea unui predecesor de viteză de comunicație 4 TWPS. putem reduce valoarea TWBR (deoarece TWBR este un octet, valoarea maximă este 255). Dar, de obicei, acest lucru nu este necesar, astfel încât TWPS stabilit, în general 0 și 4 TWPS = 1. Cel mai adesea, dimpotrivă, ne lovim în gama inferioară registrul TWBR. Dacă TWI funcționează în modul de master, atunci valoarea TWBR nu ar trebui să fie mai mică de 10. În cazul în care valoarea TWBR mai mică de 10, dispozitivul principal de autobuz poate genera semnale incorecte de pe SDA și SCL linii în timpul transmiterii de bytes.

Bit 7 - TWINT: semnalizator de întrerupere TWI

Acest steag este setat de hardware dacă TWI termină lucrarea curentă (de exemplu, transmisie, recepție de date) și așteaptă ca programul să răspundă. Linia SCL rămâne scăzută în timp ce este setat stegulețul TWINT. Steagul TWINT este resetat programabil prin scrierea în el a logicii 1. Ștergerea acestui steguleț determină reluarea TWI-ului, adică resetarea programului pentru acest steguleț trebuie efectuată după efectuarea sondajului de înregistrare a stărilor TWSR și a terminării datelor TWDR.

Bitul 6 - TWEA: Bitul de confirmare a confirmării

Bitul TWEA controlează generarea impulsului de confirmare. După cum puteți vedea în tabel, în mod implicit este resetat. Nu mă opresc, nu va fi util în acest articol.

Bitul 5 - TWSTA: Bit de stare START

Trebuie să setăm acest bit, dacă este necesar, pentru a deveni comandantul pe magistrala I2C. Cablul TWI hard verifică disponibilitatea magistralei și generează o condiție START dacă autobuzul este inactiv. Verificăm această condiție (în funcție de registrul de stare, va fi mai târziu) și dacă autobuzul este liber, atunci putem începe să lucrăm cu el. În caz contrar, va trebui să așteptați până când autobuzul este eliberat.

• Bitul Bit 4 - TWSTO: STOP bit condiție

Setarea bitului TWSTO în modul master duce la generarea unei condiții STOP pe magistrala I2C. Dacă starea STOP este îndeplinită pe magistrală, bitul TWSTO este resetat automat și magistrala este eliberată.

Bitul 3 - TWWC: Steagul înregistrării eronate

Bitul TWWC este setat când încercați să scrieți în registrul de date TWDR când TWINT este scăzut. Steagul este resetat atunci când este înregistrat registrul TWDR, când TWINT = 1.

• Bitul 2 - TWEN: bitul de activare TWI

Bitul TWEN permite operația TWI și activează interfața TWI. Dacă bitul TWEN este setat, atunci TWI preia funcțiile SCL și SDA I / O. Dacă acest bit este zero, atunci TWI este dezactivat și toate transferurile sunt terminate indiferent de starea de funcționare.

Bitul 1 - bit rezervat

Bit 0 - TWIE: întrerupeți activarea TWI

Dacă un jurnal este scris în acest bit. 1 și bitul I din registrul SREG (întreruperile sunt permise la nivel global), atunci este permisă o întrerupere de la modulul TWI (ISR (TWI_vect)) cu orice modificare a registrului de stare.

Registrul de stat TWI - TWSR

În modul transmițător, registrul TWDR conține un octet pentru transmisie. În modul Receptor, registrul TWDR conține ultimul octet primit. Aveți grijă, după setarea hardware a semnalizatorului TWINT, registrul TWDR nu conține nimic specific.

Toate funcțiile (inițializarea LST, citi, scrie memorie externă) am făcut în fișiere separate, așa cum este acceptat să facă, i2c_eeprom.c și i2c_eeprom.h.

Ei bine, cele mai importante funcții pe care le-am scris. Pe această bază, puteți scrie funcții pentru citirea / scrierea matricei de octeți. De asemenea, puteți adăuga o întrerupere ISR (TWI_INT), care va fi declanșată de fiecare dată când se schimbă registrul de stare. Voi spune doar câteva cuvinte despre acest lucru, deoarece ați înțeles cele de mai sus, nu veți fi greu să le implementați singuri.

va fi următorul text, tragem codul în buclă:

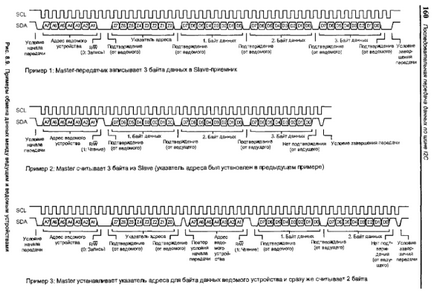

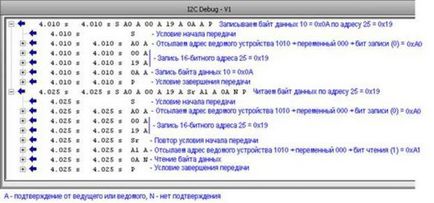

În procesul de citire schimbările vor fi un pic mai complicat, deoarece citirea între octeți de date trebuie să fie confirmarea de la maestru, și după ce a citit ultimul octet de confirmare nu ar trebui să fie, urmată de starea transmisiei este finalizată (starea STOP).

Despre intermitent ISR (TWI_INT) Nu voi spune nimic, da doar un exemplu de utilizare (de obicei acest lucru este de ajuns, totul devine clar imediat):

Tot ce rămâne rămâne să creați un proiect în AVR STUDIO:

În setările proiectului, specificați orice MEGA (de exemplu, atmega16), conectați fișierele i2c_eeprom.c și i2c_eeprom.h.

În program, am specificat în mod explicit frecvența ceasului controlerului meu de 16 Mhz. Apoi, în Proteus, vom alege un cip de memorie extern I2C EEPROM. Nu uita apoi pentru a compara setările din i2c_eeprom.h cu parametrii cip selectat (slaveF_SCL slaveAddressConst -. informații fiabile pot fi întotdeauna găsite din fișele tehnice).

Deci, rămâne să asambleze proiectul și să procedăm la modelare.

III. Simulăm munca cu EEPROM-ul I2C în Proteus

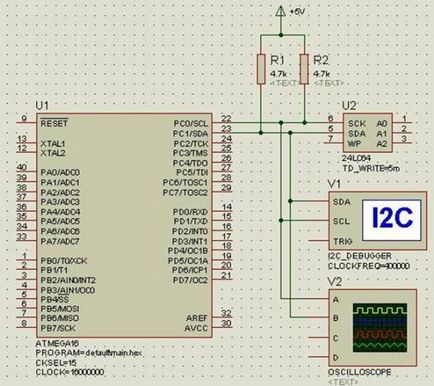

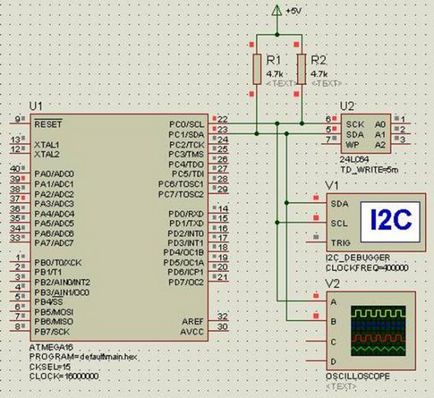

Am adăugat circuitului ATmega16, două rezistoare pentru frânarea cu autobuz I2C (vezi diagrama de la începutul articolului). Din fila Instrumente virtuale, luați Osciloscopul și Deblocerul I2C. Pentru a selecta o memorie, introduceți căutarea I2CMEMS în fereastra de selectare a dispozitivului:

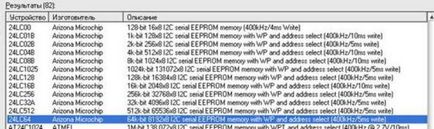

Din întreaga listă am ales 24LC64 cu memorie de 64KB și frecvență bus I2C 400KHz.

În setările controlerului, specificați firmware-ul, frecvența ceasului de 16 MHz și nu uitați să puneți CKSEL-fyuzy pentru cristal. În setările debuggerului I2C, indicați frecvența ceasului de pe busurile de 400 KHz.

Acum poți să te duci la nivelul de mai jos și să privești oscilograma:

[4] Foaie de date Microchip 24AA64 / 24LC64

Ceva pe care nu l-am copiat.

Articole similare

Trimiteți-le prietenilor: