Recent, site-ul chinez notoriu oferă să cumpere amatori de radio tot felul de carduri de depanare pe FPGA. dar, din păcate, că este disponibil pentru mintea nepregătit (sau unul care ar fi plăcut să-mi) descrierea în limba rusă (Cum funcționează?) pe Internet, nu am găsit. De-a lungul timpului, desigur, înțelegerea a venit, dar și dorința de a scrie un articol introductiv cu imagini frumoase care să explice în mod clar esența FPGA. Să începem.

FPGA - Schemă integrată logică programabilă. IMPORTANT! Există două tipuri de LSI (Large Integrated Circuit), pe care o avem în CSI corespunde definiției unui FPGA, dar cu toate acestea, principiul de funcționare al LSI este diferit, ceea ce creează disonanță cu starea reală a lucrurilor. În același timp, în Occident, în fiecare dintre LSI are destul de numele său propriu, asociind în mod clar punct I, și anume: CPLD-cip - un firmware FPGA (configurație) este întotdeauna stocate în cip în sine, iar alimentarea este oprită NICIODATĂ este șters. Pare destul de logic ca auto-piercing-ul este de a fi stocate în cip, și să se concentreze pe ea nu ar trebui să fie, ci trece la următorul LSI. Cipul FPGA este, de asemenea, un FPGA, dar configurația sa este stocată pe o sursă externă de memorie nonvolatilă (de exemplu, toate tipurile de flash). Cum funcționează? Foarte simplu, de fiecare dată când porniți, configurația FPGA se coase, care este luat din memorie și sunt șterse atunci când opriți.

Trebuie remarcat faptul că procesul de scriere la CPLD și FPGA de configurare nu este diferită: toate scrise descriere limbaj hardware VHDL sau Verilog. Apoi, există o sinteză și de punere în aplicare (compilatorul va încerca mai întâi să înțeleagă ceea ce ai scris, și apoi încearcă să plaseze toate structurile, registrele și conexiunile în FPGA, scrise pe baza), iar ultima etapă este generat .bit - fișier care este cusut pe interfata JTAG-programator în aparat.

Dacă CPLD încă cumva obișnuiți să lucreze ( „Ei bine, cum în microcontroler!“ - vă spun), apoi FPGA, cu sursele sale de neînțeles externe de memorie, par a fi niște fiare incomode, astfel încât totul de mai jos este scris va fi dedicată FPGA (dar trucuri programare sunt valabile și pentru CPLD) pentru a clarifica această problemă. Toate probele de cod vor fi executate în VHDL.

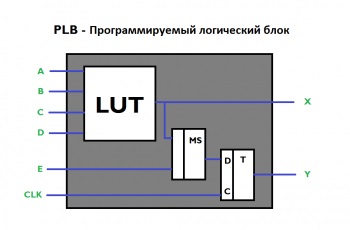

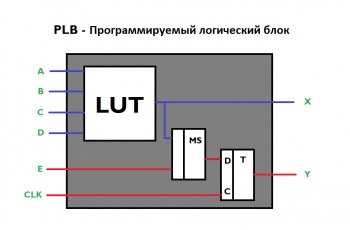

Luați în considerare cea mai mică componentă a FPGA, care se numește PLB - Bloc logic programabil.

PLB constă dintr-o tabelă de potrivire LUT, un multiplexor și un flip-flop D. Să începem cu LUT. De fapt, LUT - o memorie cu acces aleator statice (RAM -. Random Access Memory este o memorie volatilă, care este șters atunci când datele putere (inclusiv înregistrate în afara din nou, și toate datele înregistrate sunt șterse) are o rată ridicată ..... viteza), în care sunt stocate valorile de ieșire X, formate prin valorile lui A, B, C, D.

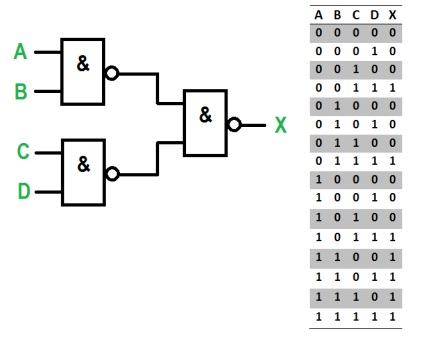

Să presupunem că trebuie să punem în aplicare pe circuitul FPGA arătat în figura de mai jos, cu tabela de adevăr corespunzătoare:

Semnale A, B, C, D sunt hrănite la intrare LUT, urmând apoi din tabela de adevăr, care este stocat în LUT, format instantaneu semnal X. Este foarte simplu. În cod se arată astfel:

X <= (A nand B) nand (C nand D);

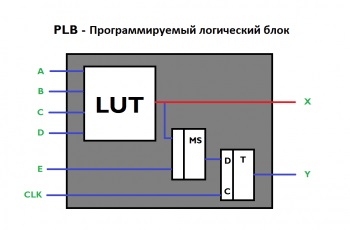

În figura de mai jos, linia roșie arată modul în care semnalul de ieșire este generat la nivelul hardware:

Dar dacă avem nevoie să sincronizăm semnalul la frecvența ceasului? Apoi, în timpul configurării scrisului, avem nevoie pentru a specifica faptul că semnalul de ieșire va fi instalat fie pe partea din față (rising_edge (clk)) sau o felie (falling_edge (clk)) de CLK semnal de ceas, iar compilatorul va prelua semnalul de ieșire ieșire c X, de la ieșirea Y. În VHDL se arată astfel:

dacă (rising_edge (clk)) atunci

Y <= (A nand B) nand (C nand D);

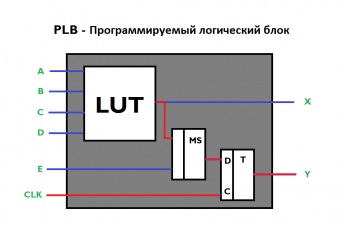

La nivel hardware, acesta este cazul: semnalul de la LUT merge la flip-flop T, care stabilește valoarea ieșirii Y la CLK.

Ce se întâmplă dacă trebuie să întârzii semnalul de intrare pentru un ciclu de ceas? Apoi, în configurație, asignăm semnalul de întârziere la semnalul nou în procesul CLK sincronizat:

dacă (rising_edge (clk)) atunci

Acest lucru se întâmplă în felul următor:

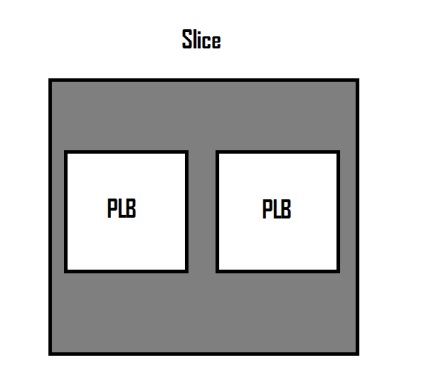

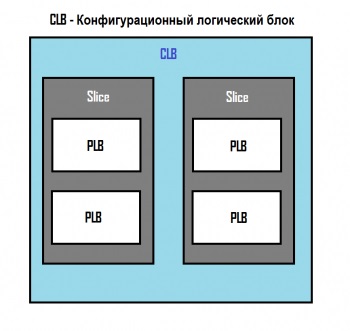

Îmi amintesc că toate cele de mai sus se întâmplă în cadrul uneia dintre cele mai recente componente ale FPGA, și anume PLB. Dar în interiorul FPGA zeci de mii de astfel de PLB (și poate sute, tehnologii sunt: nu stați liniștiți), care se pot conecta unul cu celălalt. Pentru a facilita organizarea legăturilor între ele, FPGA folosește un principiu modular: micul este mare: două PLB formează un SLICE.

În concluzie, aș dori să vă spun de ce ar trebui să te uiți la FPGA, și în special, FPGA-chips-uri. În primul rând, acesta este un câmp nelimitat pentru creativitate: aveți nevoie de un timer / contor exotic de 13 biți? - Ia-o. Necesită 15 UART? - Ușor. Trimiteți date la 6 Gbps? - nu o întrebare. Și dacă avantajele FPGA sunt evidente, atunci hai să ne mutăm la care unul este de preferat: CPLD sau FPGA? Vreau să observ că, de fapt, totul depinde de aplicație. Dacă proiectul nu este mare, dar necesită periferice specifice, atunci acesta este CPLD. Și dacă aveți nevoie de flexibilitate și viteze foarte mari, atunci acesta este FPGA. Nimic nu vă împiedică să facă acest lucru la un moment de timp, FPGA a lucrat mai întâi într-o singură versiune, dar apoi în al doilea, al treilea, al cincilea, al zecelea (proprietăți) configurabile, deoarece, spre deosebire de alte chips-uri, de înregistrare a resurselor / ștergere în FPGA tind la infinit (în cazul în care ultima dată când ați schimbat RAM în PC-ul, datorită faptului că a dezvoltat o resursă pe scriere / stergere? asta e ceea ce știu. de fapt, asta e tot, vă mulțumesc pentru atenție

Aici sunt pe link-ul dvs., a văzut placa de bază minimă cu ALTERA FPGA CycloneII instalat pe el EP2C5T144. Deci, despre ce vorbesc, pentru a folosi această placă, va trebui să conectez un cip de memorie extern la ea? Sau, firmware-ul va fi încărcat cu un blaster de fiecare dată când bordul este pornit și va funcționa până când alimentarea va fi oprită fără memorie externă?

Placa de depanare însăși are deja un cip de memorie, în cazul în care firmware-ul va fi stocat, astfel încât nu va trebui să vă lipiți personal memoria. În ceea ce privește procesul de flash, atunci când coase, mediul va va oferi de a alege în cazul în care pentru a descărca firmware-ului: în cip FPGA sau cip FLASH. Dacă încărcați FPGA, atunci da, alimentarea este oprită de firmware vor fi șterse dacă FLASH, atunci alimentarea este oprită în timpul firmware-ul va Flash, și chiar și atunci când repornirea FPGA se va încărca un firmware de FLASH, fără ajutorul ByteBlaster'a.

Pentru a răspunde, trebuie să știți în ce cantitate să cumpărați.

Dar, în general, pentru începători, pot recomanda să luați imediat un FPGA normal, mai degrabă decât un CPLD și mai mult sau mai puțin o generație modernă, de exemplu

Și pentru început este mai bine de la Altera, au un software mai adecvat și vizual.

Articole similare

Trimiteți-le prietenilor: