Organizarea de comunicare serială asincronă cu un dispozitiv extern este complicată de faptul că transmiterea și primirea de partea link-ul de serie utilizat reglate la aceeași frecvență, dar diferite fizic generatoare de impulsuri de ceas și, prin urmare, sincronizarea globală este absentă. Luați în considerare, de exemplu, organizarea controlorilor de interfață serială pentru transmisia și recepția de date asincrone în serie.

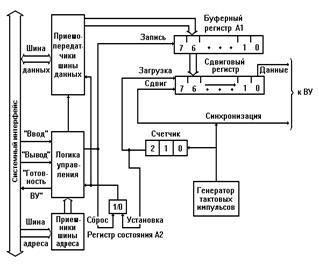

Cel mai simplu controler pentru transferul asincron al datelor către UV prin intermediul unei legături seriale este prezentat în Fig. 3.8. Este proiectat pentru a transfera datele într-un format cu doi biți de oprire.

Fig. 3.8. Controler de transfer asincron de serie

După transmiterea următorul octet de date în starea de înregistrare A2 înregistrate 1. Ieșirea A2 Unitatea de registru informează procesorul a controlerului de disponibilitatea de a primi următorul octet de date și transmiterea acestuia prin legătura de comunicații din slave. Acesta interzice același circuit de impulsuri de semnal de formare pentru a genera impulsuri de schimbare - generator de semnal de ceas compas 16. puls schimbare de frecvență counter (Contor de mod 10) este într-o stare de zero, iar semnalul de ieșire unitate este alimentat poarta SI pregătirea circuitului de generare a semnalului de sarcină registrul de deplasare .

Procesul de transmitere a unui octet de date începe cu procesorul care emite acest octet pe magistrala de date executând comanda "Output". În același timp, procesorul generează semnalul de control al interfeței de sistem "Output", care înregistrează octetul transmis în registrul tampon A1, șterge registrul de stare A2 și generează un semnal "Load" pe valvă. Bibiul transferat este rescris la biții 1. 8 din registrul de deplasare, 0 (bitul de pornire) este scris la bitul zero al registrului de deplasare și la biții 1 și 10 - 1 (biți stop). În plus, semnalul "Resetare" este scos din divizorul de frecvență, începe să acumuleze impulsuri de ceas și în momentul recepționării celui de-al șaisprezecelea impuls de tact produce un impuls de forfecare.

Pe linia de ieșire a controlerului de date, starea 0 (valoarea de început) este menținută până la generarea primului impuls de schimbare. Pulsul de forfecare va schimba starea numărătorului de impulsuri de schimbare și va suprascrie primul bit informativ al octetului de date transmis în banda zero a registrului de deplasare. Starea corespunzătoare valorii acestui bit va fi menținută pe linia "Date" până la următorul impuls de schimbare.

În mod similar, biții de informație rămași, primul bit de stop și, în final, al doilea bit de stop vor fi transmiși, la transmisia cărora contorul impulsurilor de schimbare va reveni din nou la zero. Acest lucru va duce la scrierea 1 în registrul de stare A2. Un singur semnal de la ieșirea din registrul A2 va interzice formarea impulsurilor de forfecare și, de asemenea, va informa procesorul că este gata să primească un octet de date nou. După terminarea transmisiei următorului cadru (bit inițial, octet de date și doi biți de oprire), controlerul menține nivelul liniei logice (valoarea celui de-al doilea bit de stop) din linia de comunicație.

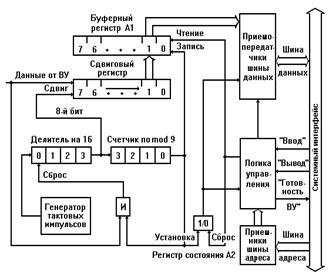

Fig. 3.9. Controler secvențial de recepție asincron

Nivelul unității logice intră în linia de date din controler pentru recepția de date asincrone (Figura 3.9). Acest nivel creează condițiile pentru generarea unui semnal care interzice funcționarea divizorului de frecvență al generatorului de ceas. Într-adevăr, după recepționarea octetului de date anterior, contorul pentru impulsurile de schimbare (contra-mod 9) este în stare zero și două intrări singulare sunt introduse la poarta AND: de la contorul de schimbare și de la linia "Date". La ieșirea porții AND, semnalul de resetare al divizorului de frecvență al semnalelor de ceas este generat, ceea ce interzice formarea impulsurilor de forfecare.

Momentul schimbării de bit de stop pentru a începe de biți (transmiterea începutul unui nou cadru) pe linia de nivel „date“ logica zero și va fi retras, prin urmare, din semnalul de resetare de divizare a frecvenței. Starea contorului binar pe 4 biți (divizor) va începe să se schimbe. Atunci când contorul acumulează o valoare de 8, acesta va transmite un semnal către intrările registrului de deplasare și la contorul de impulsuri de schimbare. Deoarece receptorul oscilator frecvența semnalului impuls de ceas trebuie să corespundă cu frecvența ceasului transmițătorului, trecerea (citire) biți apar la aproximativ intervalul de timp de mijloc alocat pentru transmiterea de biți de date, r. E. Timpul necesar pentru a genera șaisprezece impulsuri de ceas. Acest lucru se face pentru a reduce probabilitatea de eroare din cauza unei posibile generator de frecvență diferență emițător și receptor, distorsionarea semnalelor transmise (fenomene tranzitorii) și m. N. Următoarea schimbare va avea loc după trecerea ceasul șaisprezece impulsuri t. E. In mijlocul unui interval de timp de transmisie a primei informații biți.

Când luate în registrul de deplasare al biților cadru a noua (opt biți de date) de la ea „apare“ bitul de start, și, prin urmare, întregul octet de date recepționat este plasat în registrul de deplasare. În acest moment, contorul de impulsuri de schimbare vine la starea zero și un singur semnal va fi emis la ieșire, pe care conținutul registrului de deplasare poate fi rescrisă în registrul tampon, un statut registru A2 este scris 1 și va informa CPU de finalizare de primire a următorului octet și poarta se pregătească pentru generarea semnalului "Reset" (acest semnal este generat după sosirea primului bit de oprire).

După primirea semnalului gata (1 în registrul A2), procesorul va executa comanda "Enter" (a se vedea Exemplul 2.2 Transferul paralel de date). În acest caz, semnalul de comandă al interfeței de sistem "Input" este generat, prin care batetul recepționat de date este transferat din registrul tampon către procesor (semnalul "Read") și registrul de stare A2 este resetat.

Rețineți că pentru simplitatea expunerii în regulatorul din Fig. 14, circuitele de comandă a biților de stop ale cadrului primit nu sunt prezentate. Nu se arată, de asemenea, scheme sau paritate impar (paritate) informațiile care trebuie transmise (de obicei, într-un octet transmis la al optulea bit este dată valoarea 0 sau 1, astfel încât octetul a fost un număr egal de unități). În controlerele actuale sunt astfel de sisteme, iar în cazul în care operatorul nu acceptă numărul link-ul dorit de biți de stop sau semnalul de eroare de paritate generată la sistemul de paritate, datele primite în biții de cadru curente sunt ignorate, iar controlorul așteaptă un nou bit de start.

Schimbul de date cu sclavi pe linii de comunicații seriale este utilizat pe scară largă într-un microcomputer, în special în acele cazuri în care nu este necesară o viteză mare de schimb. În același timp, utilizarea liniilor succesive de comunicare cu UV în acestea se datorează două motive importante. În primul rând, liniile de comunicații seriale sunt simple în organizarea lor: două fire cu transmisie simplex și semipuplexă și maximum patru - cu duplex. În al doilea rând, microcalculatorul utilizează dispozitive externe, schimbul cu care este necesar să se desfășoare într-un cod secvențial.

În microcomputerele moderne, de regulă, sunt utilizate controale universale pentru serialul BB, care oferă atât mod sincron cât și asincron de schimb de date cu UV.

Articole similare

Trimiteți-le prietenilor: